# TECHNIQUE OF FAILURE ANALYSIS FOR GATE OXIDE DEFECT OF BI-POLAR CMOS DIFFUSE (BCD) TECHNOLOGY

Engr. FARISAL BIN ABDULLAH AAE

A thesis submitted is fulfillment of the requirement of the Degree of Master of Electrical Engineering

Faculty of Electrical and Electronic University Tun Hussein Onn Malaysia

MARCH 2013

#### ACKNOWLEDGEMENTS

In the name of Allah, The Most Gracious and The Most Merciful.

I would like to take this opportunity to convey my sincerely appreciation to my supervisors, Associate. Prof. Dr. Nafarizal bin Nayan and Associate. Prof. Dr. Muhammad Mahadi Bin Abdul Jamil for their guidance and encouragement that was given throughout of research period until the thesis preparation accomplishment. Token of appreciation to ST Microelectronics peers for their guidance and technical support, Mr. BS Teo, Mr. Norfauzi Bin Kamsin, Zukhairi Bin Md Sarip, Fausto Redigolo and Mrs. Simona Pappalardo during completed this research in ST Muar Failure Analysis laboratory. This admiration dedicates to all who are involved either directly or indirect in assisting towards the success of this research project. Hopefully, this thesis can become a guide line and source of reference to electrical engineering students in universities and failure analysis engineers in the semiconductor industry. Lastly, extraordinary dedication to my mother Hajah Khatijah Abdul Shukor, my beloved wife Engr. Siti Amely Jumaat, my children Muhammad Fadlin Aiman, Nur Farisah Amirah, and Muhammad Ammar for their prayer, endurance and being my source of inspiration.

#### ABSTRACT

This research presents failure analysis (FA) works on gate oxide defect of Bipolar CMOS Diffuse (BCD) technology. The latent problem with electrical degradation in the CMOS performance is due to gate oxide defect. The defect was well known affects the CMOS reliability after certain period of time, temperatures and stress. The FA techniques used for this research were developed using a combination of I<sub>DDQ</sub> scan test pattern, photo localization by the emission microscope and Field Emission Scanning Electron Microscopy (FE-SEM) for defect inspection. The FA methods successfully evaluated on few failing samples which were taken from customer return with IDDO failure range from 50µA until less than 1mA. Concurrently, the spotted excessive emission found on the defective samples during photo localization step indicates of gate oxide defect. The defect well observed with FE-SEM analysis on all tested samples after the physical analysis accomplishment until oxide layer. The proposed technique shows an effective method to compensate the existing FA difficulty on gate oxide defect faced by IC manufacturer in micrometer and nanometer scale technology, which having more metal interconnection layers with higher dense. The proposed technique able to construct promising result compared to the conventional techniques which used in the current FA practice due to certain extends of limitation.

#### ABSTRAK

Penyelidikan ini menerangkan mengenai analisis kegagalan pada lapisan pintu oksida bagi teknologi Bipolar CMOS Diffuse (BCD). Teknik analisis kegagalan ini menggunakan gabungan ujian data imbasan arus dalam keadaan statik (I<sub>DDQ</sub>), disamping penggunaan mikroskop foto pemancaran dan Field Emission Scanning Electron Microscopy (FE-SEM) untuk pemeriksaan kegagalan. Analisis kegagalan dilakukan dengan menggunakan sampel yang diambil daripada aplikasi pelanggan yang telah rosak dengan julat kegagalan I<sub>DDO</sub> diantara 50µA sehingga kurang daripada 1mA. Semasa analysis kegagalan dilakukan dengan menggunakan kaedah foto pemancar, lebihan cahaya yang dijumpai pada litar bersepadu yang rosak menunjukkan simptom awal yang disebabkan oleh kegagalan pada pintu pagar oksida. Kegagalan ini dapat dibuktikan semasa proses fizikal terhadap sampel dan kemudian pemeriksaan dengan menggunakan FE-SEM. Teknik analisis kegagalan ini mencadangkan satu kaedah yang lebih efektif bagi menyelesaikan permasalahan yang dihadapi oleh pengeluar IC untuk melakukan ujian kegagalan lapisan pintu oksida dalam teknologi berskala mikro dan nano. Kesimpulannya, teknik ini didapati mampu menghasilkan keputusan yang lebih baik berbanding dengan teknikteknik lazim yang digunakan sebelum ini. Ini disebabkan oleh beberapa faktor yang dikenalpasti telah menghadkan penggunaannya di dalam teknologi analisis kegagalan.

## TABLE OF CONTENT

| TITLE                 | i     |

|-----------------------|-------|

| DECLARATION           | ii    |

| ACKNOWLEDGEMENTS      | iii   |

| ABSTRACT              | iv    |

| ABSTRAK               | v     |

| CONTENT               | vi    |

| LIST OF TABLES        | X     |

| LIST OF FIGURES       | xi    |

| LIST OF ABBREVIATIONS | xvi   |

| LIST OF PUBLICATIONS  | xviii |

**CHAPTER 1**

#### INTRODUCTION 1 1.1 Research background 1 1.2 Problem statement 3 Background of current FA on 5 1.2.1 BCD technology 1.2.2 Probing Method Challenge for 6 Currently BCD FA 1.2.3 Scan test opportunity for FA on 8 CMOS VLSI Objective of study 1.3 10 Scope of work 1.4 11 1.5 Thesis outline 12

| CHAPTER 2 | LITE | RATU           | RE REVIEW                                              | 13       |

|-----------|------|----------------|--------------------------------------------------------|----------|

|           | 2.1  | Defin<br>Analy | ition of CMOS VLSI Failure                             | 14       |

|           | 2.2  | Digita         | l logic circuit and testing                            | 15       |

|           |      | 2.2.1          | ASIC device on the VLSI circuit                        | 15       |

|           |      | 2.2.2          | Digital logic test for CMOS VLSI                       | 17       |

|           | 2.3  | Digita         | l circuit fault modeling                               | 20       |

|           |      | 2.3.1          | Logical fault model                                    | 21       |

|           |      | 2.3.2          | I <sub>DDQ</sub> fault model                           | 26       |

|           | 2.4  | Fault          | coverage                                               | 29       |

|           | 2.5  | The S          | tructure of Gate Oxide (GOX)                           | 31       |

|           |      | 2.5.1          | Micro structure and bond energy of $SiO_2$             | 32<br>32 |

|           |      | 2.5.2          | Reliability of Gate Oxide in wafer                     | 33       |

|           |      | 2.5.3          | Breakdown of Gate Oxide                                | 35       |

|           |      | 2.5.4          | Gate Oxide's leakage current                           | 37       |

|           | 2.6  | Fault          | Localization Analysis                                  | 39       |

|           |      | 2.6.1          | Photo Emission Microscope<br>Principle                 | 40       |

|           |      | 2.6.2          | Field Emission Scanning<br>Electron Microscopy (FESEM) | 47       |

|           | 2.7  | Previo         | ous FA work on CMOS VLSI                               | 49       |

|           | 2.8  | Summ           | nary                                                   | 52       |

|           |      |                |                                                        |          |

| CHAPTER 3 | MET  | HODO           | LOGY                                                   | 53       |

|           | 3.1  | Fault          | localization using PEM                                 | 56       |

|           | 3.2  | ATPF           | Scan Test                                              | 57       |

|           |      | 3.2.1          | $I_{DDQ}$ scan test pattern algorithm                  | 58       |

|           |      | 3.2.2          | Measurement result of I <sub>DDQ</sub> current timing  | 62       |

|           | 3.3  | Sampl               | e Preparation                                                                         | 64       |

|-----------|------|---------------------|---------------------------------------------------------------------------------------|----------|

|           |      | 3.3.1               | Front side of sample preparation                                                      | 66       |

|           |      | 3.2.2               | Backside of sample preparation                                                        | 71       |

|           |      | 3.2.3               | Sample preparation for experiment                                                     | 80       |

|           | 3.4  | •                   | al analysis and defect identification                                                 | 81       |

|           |      | 3.4.1               | Silicon die de-processing analysis                                                    | 81       |

|           |      | 3.4.2               | FE-SEM for topography observation                                                     | 82       |

|           | 3.5  | Summ                | ary                                                                                   | 83       |

|           |      |                     |                                                                                       |          |

| CHAPTER 4 | RESU | LT AN               | D DISCUSSION                                                                          | 84       |

|           | 4.1  |                     | ftware simulation with GOX oriented                                                   | 87       |

|           |      | 4.1.1<br>4.1.2      | Ohmic soft defect on the CMOS<br>inverter<br>Ohmic soft defect on OR logic<br>circuit | 87<br>89 |

|           | 4.2  | I <sub>DDQ</sub> cu | urrent measurement result                                                             | 93       |

|           |      | 4.2.1               | Ohmic hard defect on the logic circuit                                                | 95       |

|           |      | 4.2.2               | Leakage estimation on the benchmark circuit                                           | 96       |

|           |      | 4.2.3               | Leakage timing and measurement<br>on the tested circuit                               | 97       |

|           |      | 4.2.4               | Scan test pattern on the tested circuit                                               | 102      |

|           | 4.3  |                     | emission and die level<br>aphy analysis                                               | 107      |

|           | 4.4  | Emissi              | on Result and Failure Mechanism                                                       | 112      |

|           | 4.5  | Summ                | ary                                                                                   | 114      |

| CHAPTER 5 |     | CLUSION AND<br>OMMENDATIO | N                 | 115 |

|-----------|-----|---------------------------|-------------------|-----|

|           | 5.1 | Conclusion                |                   | 115 |

|           | 5.2 | Recommendation            | n and Future Work | 117 |

|           |     |                           |                   |     |

|           | REF | ERENCES                   |                   | 119 |

|           | APP | ENDIX A                   |                   | 128 |

|           | APP | ENDIX B                   |                   | 130 |

|           | APP | ENDIX C                   |                   | 132 |

# LIST OF TABLES

| Table 2.1 | Integration levels on the digital circuit                                                                               | 15  |

|-----------|-------------------------------------------------------------------------------------------------------------------------|-----|

| Table 2.2 | Fundamental of logic gates structures                                                                                   | 17  |

| Table 2.3 | Input patterns complexity for combinational logic output                                                                | 20  |

| Table 2.4 | Type of fault localization techniques for CMOS VLSI FA                                                                  | 39  |

| Table 2.5 | FA outcome from previous work consist of tools and methods                                                              | 50  |

| Table 3.1 | CMOS VLSI IC features trend on BCD technology                                                                           | 53  |

| Table 3.2 | The microscope objective lens limitation between two methods of sample preparation                                      | 78  |

| Table 3.3 | Sample preparation summary for the defective IC                                                                         | 80  |

| Table 4.1 | The table shows how the matrix fault works based on the test vector                                                     | 86  |

| Table 4.2 | Individual MOS conditions correspond to input logic, $V_{IN}$ biasing to pull-down the current supply, $I_{DDQ}$ to GND | 89  |

| Table 4.3 | Elevate $I_{DDQ}$ current during the scan test on the fault free transistor cell                                        | 91  |

| Table 4.4 | Elevate $I_{DDQ}$ current during the scan test on the faulty transistor cell                                            | 91  |

| Table 4.5 | Leakage estimation result for benchmark circuit                                                                         | 96  |

| Table 4.6 | $I_{DDQ}$ current measurement result at different post-test time                                                        | 99  |

| Table 4.7 | $I_{\text{DDQ}}$ current measurement result at different post-test time with V-bump stress                              | 100 |

| Table 4.8 | Elevate I <sub>DDQ</sub> current result from the defective sample ICs                                                   | 101 |

# LIST OF FIGURES

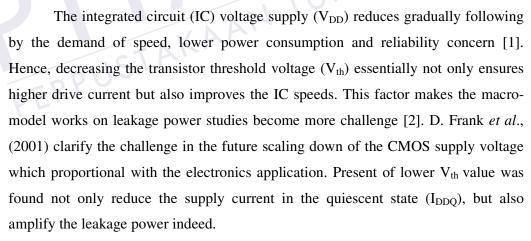

| Figure 1.1  | The reduction of gate length in lithography technology and<br>escalating of metal level influence the probing techniques due<br>to scale constraint. | 4        |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

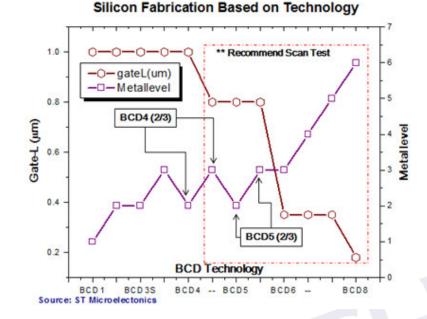

| Figure 1.2  | The lithography technologies influence the metal lines width, gap between them and space between metal layers.                                       | 6        |

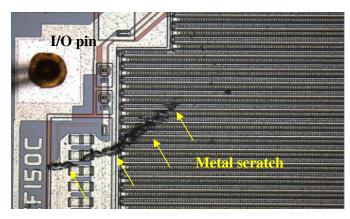

| Figure 1.3  | The example of damage on the die surface due to probing method                                                                                       | 7        |

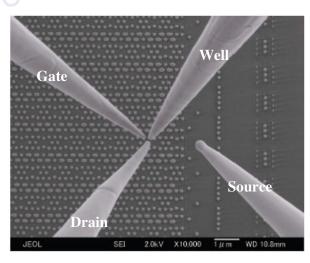

| Figure 1.4  | A SEM image showing four nano-probes at the source, drain, gate and well contacts of a transistor.                                                   | 7        |

| Figure 1.5  | Principle of open failure site detection with limited probe tip.                                                                                     | 8        |

| Figure 2.1  | The digital ICs availability                                                                                                                         | 16       |

| Figure 2.2  | Digital IC test set-up                                                                                                                               | 17<br>10 |

| Figure 2.3  | Combinational logic input and output simplified block                                                                                                | 19       |

| Figure 2.4  | The SAF model and its Boolean expression between fault free and faulty.                                                                              | 22       |

| Figure 2.5  | Circuit schematic represent the bridge fault events                                                                                                  | 24       |

| Figure 2.6  | (a) Illustration of inverter circuit proposed with gate to drain defect                                                                              | 28       |

|             | (b) $I_{DDQ}$ signature subsequent due to the leakage                                                                                                | 28       |

| Figure 2.7  | The effectiveness of $I_{DDQ}$ scan test data from HP and IBM.                                                                                       | 29       |

| Figure 2.8  | Cross section of NMOS                                                                                                                                | 31       |

| Figure 2.9  | SiO <sub>2</sub> molecules bond geometry orientation                                                                                                 | 32       |

| Figure 2.10 | Bathtub Curve for Failures                                                                                                                           | 33       |

| Figure 2.11 | 3D CMOS Inverter structure with the expected current leakage                                                                                         | 35       |

| Figure 2.12 | (a) Formation of Traps in the Gate-Oxide                                                                                                             | 36       |

|             | (b) Creation of Conduction Path through Traps in the                                                                                                 | 36       |

|             | Gate-Oxide                                                                                                                                           |          |

|             | (c) Increased Traps in Gate Oxide after Conduction                                                                                                   | 36       |

|             | (d) Cross Section of the Oxide after Hard Breakdown                                                                                                  | 36       |

xi

| Figure 2.13 | Supply voltage trend with the threshold voltage scaling impact from the scaled CMOS technology nodes.                  | 37 |

|-------------|------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.14 | The hypothetical of all possible defect models present inside<br>a CMOS inverter with equivalent schematic connections | 38 |

| Figure 2.15 | Indirect radiative transitions involving (a) Phonons<br>(b) impurities and hot carriers                                | 41 |

| Figure 2.16 | Fundamental spectra of most well-known emissions                                                                       | 42 |

| Figure 2.17 | Spectral response of commercially available image intensifiers                                                         | 43 |

| Figure 2.18 | (a) Hamamatsu Photonic PEM machine                                                                                     | 44 |

|             | (b) The microscope station of the PEM machine                                                                          | 44 |

| Figure 2.19 | Broad light spectrum wavelength                                                                                        | 45 |

| Figure 2.20 | (a) The camera sensitivity on the fault localizations tools                                                            | 46 |

|             | (b) The emission result based on camera sensitivity                                                                    | 46 |

| Figure 2.21 | FESEM schematic                                                                                                        | 48 |

| Figure 2.22 | Current sensitivity versus lateral resolution of fault localization tools                                              | 51 |

| Figure 3.1  | Overall flow for the fault localization using $I_{DDQ}$ scan test                                                      | 55 |

| Figure 3.2  | (a) and (b): The comparison between proposed technique using scan test and old technique using probe                   | 56 |

| Figure 3.3  | (a) and (b): The conceptual of scan test approach on the digital logic circuit.                                        | 58 |

| Figure 3.4  | The scan test flow on the digital logic circuit                                                                        | 60 |

| Figure 3.5  | Datalog results from the scan pattern test                                                                             | 60 |

| Figure 3.6  | Flowchart of test algorithm to senses the $I_{DDQ}$ during the test pattern running.                                   | 61 |

| Figure 3.7  | I <sub>DDQ</sub> measurement timing concept the ATE tester                                                             | 62 |

| Figure 3.8  | The BCD technology die surface view and the circuit block allocation                                                   | 65 |

| Figure 3.9  | Sample preparation equipments and steps                                                                                | 65 |

| Figure 3.10 | Expected upshot for the both sample preparation techniques                                                             | 66 |

| Figure 3.11 | (a) The fine top metal line was found missing (peel-off) after the decapsulation step                                  | 67 |

|             | (b) The fine top metal line was found missing (peel-off) after the decapsulation step                                  | 67 |

| Figure 3.12 | (a) The conventional decapsulation procedure for type of plastic mold IC package                                | 68       |

|-------------|-----------------------------------------------------------------------------------------------------------------|----------|

|             | (b) The enhance decapsulation procedure for BCD 5 and above IC technology                                       | 68       |

| Figure 3.13 | (a) to (e) Front side of sample preparation steps                                                               | 69       |

| Figure 3.14 | Digital logic view from front side analysis using 5X objective lens                                             | 70       |

| Figure 3.15 | (a) The IC package subjected for cross sectioning and examines with FE-SEM                                      | 71       |

|             | (b) The cross section view of the IC package and the thickness measurement using FE-SEM                         | 72       |

| Figure 3.16 | The opening on slug area with 3mm milling bit and the grinding consume computation                              | 73       |

| Figure 3.17 | The thinning process of removing slug and pre-from layers                                                       | 74       |

| Figure 3.18 | The remaining thickness layer after the thinning and polishing process has completed                            | 75<br>75 |

| Figure 3.19 | (a) to (d): Sample preparation step by steps result                                                             | 75       |

| Figure 3.20 | (a) Digital logic with 5X objective lens view from back side analysis using CCD camera.                         | 76       |

|             | (b) Magnification of the digital logic with 20X objective lens from back side analysis using CCD camera.        | 76       |

| Figure 3.21 | (a) Digital logic view using 1X objective lens from back side analysis using IR camera.                         | 77       |

|             | (b) Magnification of the digital logic view with 20x objective lens from back side analysis using IR camera.    | 77       |

| Figure 3.22 | Reflection loss in air-silicon interface by the incident light                                                  | 79       |

| Figure 3.23 | Incident light reflection and absorption by the silicon substrate during imaging                                | 79       |

| Figure 4.1  | The digital circuits block                                                                                      | 86       |

| Figure 4.2  | The simulation result shows the test time improvement on<br>the test mode condition compares to the normal mode | 87       |

| Figure 4.3  | Ohmic defects model present of Inverter circuit                                                                 | 88       |

| Figure 4.4  | The ohmic short model affected by the p-Ch. M1 cell by using OrCAD simulations for $I_{DDQ}$ current examines   | 90       |

| Figure 4.5  | Comparable elevated $I_{DDQ}$ between faulty and fault free circuit                                             | 92       |

| Figure 4.6  | Measurement of elevated current from $V_{\text{DD}}$ pin between the defect free and the defective IC                                         | 94  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 4.7  | Measurement of elevated current on the 90nm CMOS technology using H-SPICE simulation                                                          | 94  |

| Figure 4.8  | (a to d) Series of I-V characteristic on the defective IC versus good IC                                                                      | 95  |

| Figure 4.9  | Measurement on the $I_{DDQ}$ value for the known good IC using the Teradyne A565 tester                                                       | 97  |

| Figure 4.10 | $I_{DDQ}$ current measurement during different test temperature                                                                               | 98  |

| Figure 4.11 | Software interface of the pattern generator using LabVIEW                                                                                     | 102 |

| Figure 4.12 | Sample A: Over current failure on the defective IC                                                                                            | 103 |

| Figure 4.13 | (a) Sample B: Scan test pattern sensitizes the failure on the diagnostic (HDG2) logic monitoring circuit                                      | 105 |

|             | (b) Sample B: Scan test pattern sensitizes the failure on the diagnostic (HDG2) logic monitoring circuit                                      | 105 |

| Figure 4.14 | (a) Good IC: Scan test pattern sensitizes the failure on the digital logic circuit controlled the voltage regulator (VSO1)                    | 106 |

|             | (b) Sample C: Scan test pattern sensitizes the failure on the digital logic circuit controlled the voltage regulator (VSO1)                   | 106 |

| Figure 4.15 | (a) Sample D; Under Normal Mode, the VCC and VCCM behavior found within the spec, same as good unit                                           | 107 |

|             | (b) Sample D; Under Test Mode, the VCC and VCCM behavior found within the spec, same as good unit                                             | 107 |

| Figure 4.16 | Sample A: FA result on 800nm CMOS using PEM method<br>and defect identification using FE-SEM analysis during the<br>chemically die delayering | 108 |

| Figure 4.17 | Sample B: FA result on 1µm CMOS using PEM method<br>and defect identification using FE-EM analysis during the<br>chemically die delayering    | 109 |

| Figure 4.18 | Sample C: FA result on 600nm CMOS using PEM method<br>and defect identification using FE-SEM analysis during the<br>chemically die delayering | 110 |

| Figure 4.19 | Sample D: FA result on 350nm CMOS using PEM method<br>and defect identification using FE-SEM analysis during the<br>parallel lapping step     | 111 |

| Figure 4.20 | The intensity profile obtained from the defective OR logic | 112 |

|-------------|------------------------------------------------------------|-----|

| Figure 4.21 | Failure mechanism explained the physical defect            | 113 |

# LIST OF ABBREVIATIONS

xvi

| AFP    | -    | Atomic Force Probe                                                                           |

|--------|------|----------------------------------------------------------------------------------------------|

| APG    | -    | Automotive Product Group                                                                     |

| ATE    | -    | Automatic Test Equipment                                                                     |

| ATPG   | -    | Automated Test Program Generation                                                            |

| BCD    | -    | Bipolar CMOS DMOS                                                                            |

| BGA    | -    | Ball Grid Array                                                                              |

| BICS   | -    | Built In Current Sensor                                                                      |

| CCD    | -    | Charge Couple Device                                                                         |

| CMOS   | -    | Complementary Metal Oxide Semiconductor                                                      |

| CPU    | -    | Central Processing Unit                                                                      |

| DfT    | -    | Complementary Metal Oxide Semiconductor<br>Central Processing Unit<br>Design for Testability |

| DUT    | -    | Device under Test                                                                            |

| EOS    | -    | Electrical Over Stress                                                                       |

| ESD    | -    | Electro Static Discharge                                                                     |

| EMI    | 1-15 | Electro Magnetic Interference                                                                |

| EWS    | -    | Electrical Wafer Sort                                                                        |

| FA     | -    | Failure Analysis                                                                             |

| FE-SEM | -    | Field Emission Scanning Electron Microscopy                                                  |

| FT     | -    | Final Test                                                                                   |

| GND    | -    | Ground                                                                                       |

| GOX    | -    | Gate Oxide                                                                                   |

| HSPICE | -    | High Simulation Program with Integrated Circuit Emphasis                                     |

| HVM    | -    | High Volume Manufacturing                                                                    |

| IC     | -    | Integrated Circuit                                                                           |

| I/O    | -    | Input Output                                                                                 |

| I/V              | -  | Current/Voltage                                                            |

|------------------|----|----------------------------------------------------------------------------|

| I <sub>DDQ</sub> | -  | Supply current in the quiescent state                                      |

| IMD              | -  | Intermediate Metal Dielectric                                              |

| I.V              | -  | Current Voltage measurement                                                |

| LVS              | -  | Layout versus Schematic                                                    |

| MiNT-SRC         | -  | Microelectronics and Nanotechnology-Shamsuddin Research                    |

|                  |    | Centre                                                                     |

| MOSFET           | -  | Metal Oxide Semiconductor Field Effect Transistor                          |

| NIR              | -  | Near Infra Red                                                             |

| OrCAD            | -  | Software tools for electronic design automation                            |

| PIQ              | -  | Polymide Isoindro Quirazorindione                                          |

| PMD              | -  | Pre-Metal Dielectric                                                       |

| PMU              | -  | Precision Measurement Unit                                                 |

| PTS              | -  | Precision Measurement Unit<br>Power Train and Safety<br>Quantum Efficiency |

| Q.E              | -  | Quantum Efficiency                                                         |

| SA0              | -  | Stuck At '0'                                                               |

| SA1              | -  | Stuck At '1'                                                               |

| SEM              | -  | Scanning Electron Microscopy                                               |

| SPI              | 92 | Serial Peripheral Interface                                                |

| SDI              | -  | Serial Data In                                                             |

| SDO              | -  | Serial Data Out                                                            |

| TPG              | -  | Test Program Generation                                                    |

| UTHM             | -  | Universiti Tun Hussein Onn Malaysia                                        |

| VLSI             | -  | Very Large Scale Integration                                               |

| P-MOS            | -  | P channel MOS                                                              |

| N-MOS            | -  | N channel MOS                                                              |

| $V_{DD}$         | -  | Voltage Supply                                                             |

| V <sub>SS</sub>  | -  | GND path                                                                   |

|                  |    |                                                                            |

xvii

#### LIST OF PUBLICATION

- 1. Farisal Abdullah, Nafarizal Nayan, Muhammad Mahadi Abdul Jamil, and Norfauzi Kamsin : "IDD scan test method for fault localization technique on CMOS VLSI failure analysis", ICSE Proc. 2010, Melaka.

- Farisal Abdullah, Nafarizal Nayan, and Muhammad Mahadi Abdul Jamil : "Failure analysis using IDD current leakage and photo localization for gate oxide defect of CMOS VLSI", SCORED 2010, Putrajaya.

### **CHAPTER 1**

#### **INTRODUCTION**

#### 1.1 **Research background**

MINA Since the last two decades, electronic industry has growth rapidly. Demand from the numerous segments of industries such as computing, automotive, telecommunication, and industrial product, results the microelectronics evolution become more complex.

Impact from this evolution, I<sub>DDQ</sub> current may found undersized and become more complex to discriminate between the good and fail IC. Thus, screen method at the production test also needs to be revising [3]. On the other hand, failure analysis (FA) method needs more creativity to compensate the trend as well [4-8]. As a progress, David P. Vallet (2002) has presented the FA requirement on the

nanoelectronics IC technology, which elaborates this concern. The FA challenges and techniques may penetrate a new chapter of IC diagnostic evolution [9]-[10].

Hurst S, (1998) and Bushnell M and Agrawal V, (2000) emphasize the scan test that become vital elements on the modern digital and mixed-signal VLSI circuit testing [11]-[13]. Rochit Rajsuman, (2000) further elaborate by incorporate the  $I_{DDQ}$  test into the scan test algorithm contribute significant yield improvement on the integrated circuit quality [14]. Thus these test combination makes the overall scan test become efficient to resolve the digital circuit performance especially to monitor the earlier gate oxide (GOX) failure.

The increasing number of GOX failure due to wear out phase has motivate further researcher to improve the existing wafer process and explorer new process method. The typical factors that brought out the IC become fail are during stress condition in the application environment. Therefore, there is strong requirement to develop a new approach on the specific FA technique to detect GOX defect on BCD integrated circuit. The improvement is to recommend an alternative solution for the scan failure which typically occurs on the digital logic circuit, by using proposed method cited from Design for Testability (DfT) methodology.

#### **1.2 Problems statement**

In failure analysis terminology, probe technique becomes one of the well-known methods to perform signal analysis on the BCD technology device [15]. This technique has an ability to perform signal acquisition from the probe pad, restricted logic block until to the single transistor cell. However, due to limitation on it sizes and cost, evolution on the modern FA method has progressively challenged this technique.

In existing market, the most fashionable probes are active probe and passive probe which available in several size, micro, nano and pico. The selection on it size is relying on the tested circuit been done. For single transistor cell measurement, the most accurate tool been use in nowadays FA technique is Atomic Force Probe (AFP). This technique is viable to perform comprehensive current-voltage (I-V) characteristic of the single cell which consists of Drain, Gate, Source and Well. However in term of cost-effective method AFP was consider costly compared with probe technique.

Figure 1.1 shows reduction of the gate length in BCD technology and escalating of metal interconnection levels in parallel. This combination has challenge the gate oxide reliability since the device will perform faster during switching operation. Therefore, restriction on the gate oxide failure makes the probe method become ineffective to localize the defect during FA. Modern lithography process on the BCD device is dramatically shirked from millimetre, down to below 90nm scale. This factor contributes complication on the FA method during perform a signal analysis on the micro block circuit which consist of latches and combinational logic.

Figure 1.1: The reduction of gate length in lithography technology and escalating of metal level influence the probing techniques due to scale constraint [16].

This research recommends using the  $I_{DDQ}$  scan test which typically used for the IC testing as a FA method.  $I_{DDQ}$  scan test is incorporate from the Automatic Test Pattern Generation (ATPG) method which able to stimulated limited of test vectors with higher fault coverage. This scan test is particularly to exercising the P-MOS and N-MOS transistor switching on the latches and combination logics, whereby any leaky transistor junction can be identify during the fault localization.

Failure analysis is a combination of few steps of procedure to define the possible root cause which occurs on the defective IC. The FA method may consist of combination between the testing information and appropriate diagnosis step to identify the physical defect on the IC based on the failure mode [17]. The FA method could be varies, depend on how complex the device was failed and challenge to replicate the failure mode for FA purpose.

In most events, FA becomes crucial constructive steps to translate the failure mode into an isolated area. Hereby it becomes an evolution process from the past experienced data, present use and future challenge [18].

#### **1.2.1** Background of current FA on BCD technology.

During FA, to perform fine signal characterization on the restrict logic cell; failure analyst has to perform extra probing method on the test point besides using the external leads for voltage supply and others input/output (I/O) pins.

Typically, the test points are visible on the silicon, and they are locating at the same level as the bond pad area. The visible points are not covering by the protection layer to make it easy to contact with. The main purpose to have these test points is after the wafer fabrication process is completed, every single die inside the wafer has to undergo parametric test to validate whether it has been fabricated with correct recipe according to spec or not. This test screen at the wafer side is known as an electrical wafer sort (EWS). In this case, the numbers of test points are limited and only covering the overall parameters of the die, and not to extend until the logic cell functionality. Therefore, it is essential to have more electrical information in order to drive the defect localization during the FA works [19].

In order to overcome this challenge, failure analyst has to access underneath interconnection in order to obtain the desired signal. This signal measurement can be used by the combination between laser-cut tool and active or passive probe tip. The advantage of using probing technique is, it has to provides electrical contact directly to the restrict logic block. Commonly the desired interconnection layer are present at underneath layer where all the transistors been connected together after it been fabricated deeply in the active area [20]. Takeshi Nokuo *et al.*, (2007) and S.L Toh *et al.*, (2007), propose a conducive FA method using probing technique on nanometre device to demonstrate the probing competency.

Nevertheless, the main constraint is that not all the test points are utilize for IC diagnose in particular for scan type of failure. Even though the unforeseen underneath interconnection net is possible to reach by using probing method, uncomplimentary it may create signal distortion or interference from untested digital block inside the same IC. In few specific types of failing IC which related to the digital CMOS circuit, this method found impractical to utilize for failure analysis at all. Figure 1.2 shows the illustration of few critical points on the interconnection, concise of gap, width, and level, whereas compulsory for the probing method to obtain the signals during the failure analysis works.

#### CMOS cross sectioning

Figure 1.2: The lithography process describe the metal lines width, gap between them and space between metal layers [15].

#### 1.2.2 Probing Method Challenge for Currently BCD FA.

MINA For FA step using probing method, few constrain factors were identified as the metal interconnection increase on the BCD technology. In other words, this method has a tendency to cause damaged on the silicon and only limit to a few numbers of signal measurement per one time, i.e. I-V characteristic. During this step, there is a critical path that may induce damaged on the IC surface. The step begins when the probe tip starts moving from the zero position towards the desired probing points, either on the silicon or at particular underneath the metal line (after considered the top protection layer been removed using the laser-cut method).

In worst case simulation, if the probe tip has found unintentionally vibrate or wrongly positioning on the target point due to mishandling (by human factor) or vibration on probing station (by equipment stability factor), it may result of massive interconnection damaged. Figure 1.3 shows an evident in the interconnection damage result from the worst-case simulation due to mishandling event.

Figure 1.3: The example of damage on the silicon due to probing method [21].

As a consequence, the IC becomes malfunction by default and no longer can operate as the pre-probing step. The internal circuit of the IC probably can be either 'open' or 'short' circuit. This unforeseen circumstance becomes a fear to the analyst or FA engineer since commonly the numbers of failing sample for this specific failure mode are limited.

Another point in probing method is it only can acquire a limited number of signal measurements due to constraint between the probes versus probe point. Figure 1.4 shows the limitation on the nano-probe competency during the signal measurement on the restrict circuit. The signal measurement using limited numbers of nano-probes were only works on the desired transistor or logic circuit. Thus it is not well proficient to use in larger digital logic block [15,20].

Figure 1.4: A SEM image showing four nano-probes at the source, drain, gate and well contacts of a transistor cell [20].

#### REFERENCES

[1] D. Frank, R. Dennard, E. Nowak, P. Solomon, Y. Taur, and H-S Wong. "Device scaling limits of Si MOSFETs and their application dependencies," Proc. IEEE, vol. 89, no. 3, pp. 259-288, Mar. 2001.

[2] Shengqi Yang, et al.: "Accurate Stacking Macro-modeling for Leakage Power in Sub-100nm Circuits", IEEE VLSID 2005.

[3] C.P. Ravikumar and Rahul Kumar: "Divide-and-Conquer IDDQ Testing for Core-based System Chips", VLSID, page 761, ASP-DAC/VLSI Design 2002.

[4] Christian Boit: "Can Failure Analysis Keep Pace With IC Technologies Development?", Proceedings of 7th IPFA '99, Singapore.

[5] Richard E. Anderson, Jerry M. Soden, Christopher L. Henderson, and Edward I. Cole Jr.: "Challenges For Ic Failure Analysis-Present And Future", 5th ZPFA '95: Singapore

MINA [6] Anne Gattiker: "Diagnosis Meets Physical Failure Analysis: How Long Can We Succeed?", International Proceedings ITC 2004Test Conference, 2004

[7] Chia-Chi Ho and Jeng-Han Lee: "Electrical Diagnosis and Failure Analysis on Tree Structure Circuit", Proceedings of 11th PFA 2004, Taiwan

[8] S.P. Neo, Z.G. Song, C.K Oh and S. P. Zhao: "Failure Analysis of A Unique Poly Defect", ICSE2006 Proc. 2006, Kuala Lumpur, Malaysia

[9] Lawrence C. Wagner: "Failure Analysis Challenges", Proceedings of 8" IPFA 2001, Singapore

[10] Giovanna Mura and Massimo Vanzi: "Failure Analysis of Failure Analyses: The Rules of the Rue Morgue, Ten Years Later", IEEE Transactions On Device And Materials Reliability, Vol. 7, No. 3, September 2007

[11] Thomas W. Bartenstein: "Diagnostics vs. Failure Analysis", ITC International Test Conference, 2004

[12] Hurst S., "VLSI Testing digital and mixed analogue/digital techniques", IEEE, 1998, ISBN 0-85296-901-5

[13] Bushnell M. and Agrawal V., Essentials of Electronics Testing for Digital, Memory & Mixed-Signal VLSI Circuit", Kluwer Academic Publisher, 2000, ISBN 0-7923-7991-8.

[14] Rochit Rajsuman: "IDDO Testing for CMOS VLSI", Proceedings of the IEEE, vol. 88, no. 4, April 2000

[15] S.L. Toh, Z.H. Mai, P.K. Tan, E. Hendarto, H. Tan, Q.F. Wang, J.L. Cai, Q. Deng, T.H. Ng, Y.W. Goh, J.Lam, L.C. Hsia: "Use of Nanoprobing as the Diagnostic Tool for Nanoscaled Devices", Proceedings of 14th IPFA 2007, Bangalore, India

[16] Technology roadmap for BCD technology devices – Automotive Product Group (APG), ST Microelectronics Sdn Bhd.

[17] James C.M. Li and Edward J. McCluskey: "I<sub>DDQ</sub> Data Analysis Using Current Signature", I<sub>DDQ</sub> Testing Proceedings. 1998 IEEE International Workshop

[18] Jaume Segura and Charles F.Hawkins : "CMOS Electronics – How It Works, How It Fails", Wiley-Interscience ISBN 0-471-47669-2, 2004, page(s) 290-292.

[19] Zoran Stanojevic, Hari Balachandran, D. M. H. Walker, Fred Lakhani, Sri Jandhyala: "DefectLocalizationUsingPhysicalDesign and ElectricalTestInformation", Advanced Semiconductor Manufacturing Conference 2000.

[20] Takeshi Nokuo, Yoshiyuki Eto, Zane Marek: "A New Method For Failure Analysis With Probing System Based On Scanning Electron Microscope", 45th Annual International Reliability, Physics Symposium, Phoenix, 2007

[21] FA Method and Equipments – Automotive Product Group (APG) Laboratory, ST Microelectronics Sdn Bhd.

[22] Y. Y. Chew, K. H. Siek and W. M. Yee: "Novel Backside Sample Preparation Processes for Advanced CMOS Integrated Circuits Failure Analysis", Proceedings of 7th IPFA '99, Singapore.

[23] Silke Liebert: "Failure Analysis from the Back Side of a Die", Conference Proceedings of the 26th Intenational Symposium for Testing and Failure Analysis; pages 177-185, I STFA 2000.

[24] Ang Ghim Boon, Chan Choon Kit. Chua Kok Keng and Oh Chong Khiam: TetraMax Diagnosis and Laker Software on Failure Analysis For ATPG/Scan Failures, Proceedings of 13th IPFA 2006, Singapore.

[25] Ian A.Grout: "Integrated Circuit Test Engineering", Springer, 2006.

[26] J. Sziray, "Logic testing of CMOS structures", Computational Cybernetics, 2004. ICCC 2004.

[27] Manoj Sachdev, Jose Pineda de Gyvez, "Defect-Oriented Testing for Nano-Metric CMOS VLSI Circuits", Springer, 2007.

[28] Swarup Bhunia, Hai Li and Kaushik Roy: "A High Performance  $I_{DDQ}$  Testable Cache for Scaled CMOS Technologies", Proceedings of the 11th Asian Test Symposium, 2002.

[29] Yu Huang, Wu-Tung Cheng, Janusz Rajski: "Compressed Pattern Diagnosis For Scan Chain Failures", International Test Conference IEEE 2005

[30] Ian A.Grout: "Integrated Circuit Test Engineering", Springer, 2006, page(s) 1-13.

[31] David P. Vallett: Failure Analysis Requirement for Nanoelectronics, IEEE Transaction on Nanoelectronics, Vol. 1, No. 3 September 2002.

[32] Ernst Aderholz: "Efficient Method of Debug of ATPG Scan Chain Failures on ATE", 6<sup>th</sup> IEEE International Workshop on Silicon Debug and Diagnosis, March 12<sup>th</sup> 2010.

[33] Kaushik Roy and Kwang-Ting Cheng: "Test Consideration for Nanoscale CMOS Circuits", Volume 23, Issue2, Page(s) 128-136, March 2006,

[34] Nigh, P., Vallett, D., Patel, P., Wright, J., Motika, F., Forlenza, D., Kurtulik, R., Chong, W: "Failure Analysis of Timing and IDDQ-only Failures from the AMINA SEMATECH Test Methods Experiments", Test Conference, 1998, Page(s): 43 - 52

[35] Makar, S.R, and McCluskey E.J : "Some Fault Need an I<sub>DDO</sub> Test", IDDQ Testing, 1996, Page(s): 102 – 103

[36] Sur-Kolay, S.; Dasgupta, P.; Bhattacharya, B.B.; Zachariah, S.T., "Physical design trends and layout-based fault modeling VLSI Design" 2004. Proceedings. 17th International Conference.

[37] Xinyue Fan; Moore, W.; Hora, C.; Gronthoud, G: "Stuck-open fault diagnosis with stuck-at model" Test Symposium, 2005. European .

[38] Ryan, C.A.: "On the complexity of bridging fault simulation techniques for CMOS integrated circuits ASIC" Conference and Exhibit, 1995. Proceedings of the Eighth Annual IEEE International.

[39] Ma, S.; Shaik, I.; Fetherston, R.S: "A comparison of bridging fault simulation methods", Test Conference, 1999. Proceedings. International.

[40] Sar-Dessai, V.R.; Walker, D.M.H.: "Resistive Bridge fault modeling, simulation and test generation" Test Conference, 1999.

[41] Natarajan, S.; Patil, S.; Chakravarty, S.: "Path delay fault simulation on large industrial designs", VLSI Test Symposium, 2006. Proceedings. 24th IEEE Publication Year: 2006

[42] Al-Ars, Z.; Hamdioui, S.; Gaydadjiev, G.: "Precise Identification of Memory Faults Using Electrical Simulation" Design and Test Workshop, 2007. IDT 2007. 2nd International

[43] Arumi, D.; Rodriguez-Montanes, R.; Figueras, J.: "Experimental Characterization of CMOS Interconnect Open Defects", 2008 Computer-Aided Design of Integrated Circuits and Systems, IEEE Transactions.

[44] Yuichi Sato, Hiroshi Takahashi, Yoshinobu Higami, Yuzo Takamatsu: "Failure Analysis of Open Faults by Using Detecting/Un-detecting Information on Tests", Proceedings of the 13<sup>th</sup> Asian Test

[45] Makar, S.R., and McCluskey E.J: "IDDO Test Pattern Generation for Scan Chain Latchs and Flip-Flops", IEEE International Workshop on IDDQ Testing, 1997/1997

[46] Reaz, M.B.I.; Yasin, F.M.; Sulaiman, M.S.; Ali, M.A.M: "The simultaneous logic and I<sub>DDO</sub> testing of CMOS ICs with mixed-mode testing facility for sequential circuits", Semiconductor Device Research Symposium, 2003.

[47] A. Toukmaji, R. Helms, R. Makki, W. Mikhail and R toole: "I<sub>DDO</sub> Testing Experiments for Various CMOS Logic Design Structures", VLSI Design 1997, Vol. 5. No. 3

AMINA [48] Bin Xue and D. M. H. Walker, "Built-in Current Sensor for IDDO Test", Proceedings of the 2004 IEEE International Workshop on Defect Based Testing, 2004.

[49] Kyung Ki Kim, Yong-Bin Kim, Minsu Choi, and Nohpill Park: "Accurate Macro-modeling for Leakage Current for IDDO Test", 2007

[50] B. Straka, H. Manhaeve, J. Vanneuville, M. Svajda: "A fully digital controlled off-chip I<sub>DDO</sub> measurement unit", Proceedings of the conference on Design, automation and test in Europe, 1998.

[51] Mohd Liakot Ali and Nurul Huda Khamis, "Design of a Current Sensor for I<sub>DDO</sub> Testing on CMOS IC", American Journal of Applied Sciences 2 (3): Page(s) 682-687, 2005

[52] Jing-Jou Tang, Bin-Da Liu, and, Kuen-Jong Lee: "An I<sub>DDQ</sub> Fault Model to Facilitate the Design of Built-In Current Sensor (BICSs)", Circuits and Systems, 1995. ISCAS '95., 1995 IEEE International Symposium on Volume: 1

[53] Chintan Patel, Abhishek Singh and Jim Plusquellic: "Defect detection under Realistic Leakage Models using Multiple IDDO Measurements", Test Conference, 2004. Proceedings. ITC 2004. International

[54] S. Matakias (1), Y. Tsiatouhas(2), A. Arapoyanni(1), Th. Haniotakis(3), G. Prenat(4) and S. Mir(4): "A Built-In IDDQ Testing Circuit, Proceedings of ESSCIRC, Grenoble, France, 2005

[55] Koichi Nose and Takasayu Sakurai: "Current Sensing Device for Micro-IDDQ Test", Electronics and Communication in Japan, Part 2, Vol.84, No.9, 2001

[56] VTS-ITC publication IBM Micro news and IEEE D&T, 1999

[57] Hans Manhaeve, Joseph S. Vaccaro, Loren Benecke, David Prystasz: "A Real world Application Used To Implement A True IDDQ Based Test Strategy (Facts and Figures)", IEEE European Test Workshop ETW.2002 . 26.29/05/2002, Corfu, Greece

[58] Yoshinobu Higami; Kewal K. Saluja; Hiroshi Takahashi; Yuzo Takamatsu: "Fault Coverage and Fault Efficiency of Transistor Shorts using Gate-Level Simulation and Test Generation VLSI Design", 6<sup>th</sup> International Conference on Embedded Systems 2007.

[59] Chih-Tang Sah: "Fundamentals of Solid-State Electronics", World Scientific, ISBN 981-02-0637-2. -- ISBN 981-02-0638-0 (pbk).

[60] J.McPherson and H.Mogul, "Disturbed bonding states in SiO<sub>2</sub> thin-films and their impact on time-dependence dielectric breakdown," in International Reliability Physics Symposium (IRPS), pp.47-56, April 1998.

[61] HC How, KB Ooi, JC Ng, Mohd Khairul Nizam and HB Ng: "An Innovative Gate Oxide Characterization Technique in the Failure Analysis of 0.13µm Process Technology Based MOSFET Device", Proceedings of 12th IPFA 2005, Singapore

[62] Navid Azizi, Peter Yiannacouras: "Gate Oxide Breakdown", December 2, 2003

[63] J.Segura, C.Benito, A Rubio and C.F. Hawkins, "A Detailed Analysis of GOS Defects in MOS Transistors: Testing Implications at Circuit Level," Proceedings of International Test Conference, 1995, page(s).544-551.

[64] Dave Rubiin and Yuegang Zhao : "Wafer Level Reliability Testing – A Critical Device and Process Development Step", May 2005, www.keithley.com/data?asset=15957

[65] J.H.Suehle, "Ultra thin gate oxide reliability: physical model, statistic, and characterization," IEEE Trans. Electron Devices, vol.49. 958-971, June 2002.

[66] J.W. McPERSON, Physics and Chemical of Intrinsic Time-Dependent Dielectric Breakdown in SiO2 Dielectric, 2001. International Journal of High Speed Electronics and System, Vol.11, No.3 (2001)

[67] Kunhyuk Kang, Keejong Kim, Ahmad E. Islam, Muhammad A. Alam, and Kaushik Roy: "Characterization and Estimation of Circuit Reliability Degradation under NBTI using On-Line I<sub>DDQ</sub> Measurement", DAC '07. 44th ACM/IEEE Design Automation Conference, 2007.

[68] S.F.Wan Muhammad Hatta, N.Soin and J.F.Zhang : "The Effect of Gate Oxide Thickness and Drain Bias on NBTI Degradation in 45nm PMOS", ICSE2010 Proc. 2010, Melaka.

[69] S.F.Wan Muhammad Hatta, N.Soin and J.F.Zhang : "The Effect of Process Variation on NBTI Degradation in 90nm PMOS", ICSE2010 Proc. 2010, Melaka.

[70] C K Oh Member IEEE, H T Teo, K F Lo: "A New and Effective Method in Failure Analysis of Gate Oxide Poly silicon Capacitor Structure", ICSE2004 Proc. 2004, Kuala Lumpur, Malaysia

[71] D.J. DUMIN "Oxide Wearout, Breakdown, and Reliability", International Journal of High Speed Electronics and System, Vol.11, No.3 (2001), pp.617-718.

[72] C.F Hawkins, J.M Soden, "Reliability and Electrical Properties of Gate Oxide Short in CMOS IC Testing", Proceedings of International Test Conference, 1994, pp.413-425.

[73] Jerry M. Soden and Richard E. Anderson: "IC Failure Analysis: Techniques And Tools For Quality And Reliability Improvement", the proceedings of the IEEE, Vol.81, No.5, pp.703-715, May 1993.

[74] Dongwoo Lee, et al.: "Analysis and Minimization Techniques for Total Leakage Consideration Gate Oxide Leakage", Page(s) 175-180.DAC 2003.

[75] Yong Moon Kim, Tze Wee Chen, Yoshio Kameda, Masayuki Mizuno, and Subhasish Mitra: "Gate-Oxide Early-Life Failure Identification using Delay Shift", MINA 2010 28<sup>th</sup> IEEE VLSI Test Symposium.

[76] A.Agarwal, S.Mukhopdhyay, et al.: "Leakage Power Analysis and Reduction: Models, Simulation and tools", IEEE Proc. Computer. Digit. Tech. Vol. 152, No.3, May 2005

[77] Colm Durkan "Current At The Nanoscale – An Introduction To Nanoelectronics", Imperial College Pres, Page(s) 32-35, 44-46, 2000.

[78] Kaushik Roy, Saibal Mukhopadhyay, et al.: "Leakage Current Mechanism and Leakage Reduction Techniques in Deep-Submicronmeter CMOS Circuits", Proceeding of the IEEE, Vol.91, No.2, February 2003.

[79] HeungJun Jeon, Yong-Bin Kim, and Minsu Choi: "Stanby Leakage Power Reduction Technique for Nanoscale CMOS VLSI Systems", IEEE Transaction on Instrument and Measurement, Vol.59, 2010.

[80] Sziray, J.Computational Cybernetics: "Transistor-level test calculation for CMOS circuits". ICCC 2009.

[81] Hao Chen; Jie Han; Lombardi, F.: "A Transistor-Level Stochastic Approach for Evaluating the Reliability of Digital Nanometric CMOS Circuits Defect and Fault Tolerance VLSI and Nanotechnology Systems (DFT)", 2011 IEEE International Symposium

[82] Pankove, J I(ed): "Electroluminescence" (Topics in Applied Physics vol.17) Springer, Berlin, 1977.

[83] Pankove, JI: "Optical Processes in Semiconductors", Dover, New York, 1971.

[84] Herzog, M et al: "Solid State Electronics", 1992.

[85] Kozler, J et al: "Jour. appl Phys 71"1992

[86] Chim, W K: "Semiconductor Device and Failure Analysis", Wiley, 2001.

[87] User Manual, Hamamatsu PHEMOS-1000 Photonics K.K. Document number: 55340-110-12.

[88] Oh Chong Khiam, Wu Zong Min, Shailesh Redkar, Christopher Cheong, Thomas Yang: "A New Fluorescent and Photoemission Microscope for Submicron VLSI IC Failure Analysis", ICSE2002 Proc.2002, Penang, Malaysia

[89] Lim Soon, Dawn Tan Mei Ling, Marcus Kuan, Kwong Weng Yee ,Daniel Cheoog & Galor Zhang: "Application of IR-OBIRCH to the Failure Analysis of CMOS Integrated Circuits", Proceedings of 10<sup>th</sup> IPFA 2003, Singapore

[90] Loh Ter Hoe, Yee Wai Mun, and Chew Yin Yan: "Characterization and Application of Highly Sensitive Infra-Red Emission Microscopy for Microprocessor Backside Failure Analysis", Proceedings of 7<sup>th</sup> IPFA '99, Singapore.

[91] F. Beaudoin', G. Imbed, P. Perdu', C. Trocque: "Current Leakage Fault Localization Using Backside Obirch", Proceedings of 8" IPFA 2001, Singapore.

[92] Loh Ter Hoe, Yee Wai Mun, and Chew Yin Yan: "Characterization and Application of Highly Sensitive Infra-Red Emission Microscopy for Microprocessor Backside Failure Analysis", Proceedings of 7th IPFA '99, Singapore

[93] Lim Soon, Dawn Tan Mei Ling, Marcus Kuan, Kwong Weng Yee ,Daniel Cheoog & Galor Zhang: "Application of IR-OBIRCH to the Failure Analysis of CMOS Integrated Circuits", Proceedings of IHh IPFA 2003, Singapore

[94] JCH Phang, DSH Chan, M Palaniappan, JM Chin, B Davis, M Bruce, J Wilcox, G Gilfeather, CM Chua, LS Koh, HY Ng, SH Tan: "A Review of Laser Induced Techniques for Microelectronic Failure Analysis", Proceedings of 11<sup>th</sup> IPFA 2004, Taiwan.

[95] Sz-Chian Liou, Jung-Hsiang Chuang, and Lee, J.C.: "The physical failure analysis (PFA) of  $I_{DDQ}$  and  $I_{DDQ\_delta}$  fail in 90nm logic products", Physical and Failure Analysis of Integrated Circuits, 2005 (IPFA 2005) Page(s):47–51

[96] Z. G. Song, S. K. Loh, S. P. Neo, X. H. Zheng and H. T. Teo: "Application of FIB Circuit Edit and Electrical Characterization in Failure Analysis for Invisible Defect Issues", Proceedings of 13th IPFA 2006, Singapore

[97] Xiaojun Li, Jin Qi, Bing Huang, Xiaohu Zhang, and Joseph B.Bernstein: "A New SPICE Reliability Simulation Simulation Method for Deep Submicrometer CMOS VLSI Circuits", IEEE Transactions on Device and Materials Reliability, Vol.6,No.2, June 2006.

[98] Jaffari.J, and Afzali-Kusha, A : "A Novel Technique for Reducing Leakage Current of VLSI Combination Circuit", Microelectronics, 2004. (ICM 2004), Page(s): 207 - 210

[99] Miljana Sokolovic, Predrag Petkovic, Vanco Litovski : "Design for Testability for SoC Based on IDDO Scanning", PROC. 26th International Conference On Microelectronics (MIEL 2008), NIŠ, Serbia, 11-14 May, 2008.

[100] Swarup Bhunia, Hai Li and Kaushik Roy : "A High Performance I<sub>DDO</sub> Testable Cache for Scaled CMOS Technologies", Test Symposium, 2002. (ATS '02). Proceedings of the 11th Asian

[101] ATE for BCD technology devices - Automotive Product Group (APG), ST Microelectronics Sdn Bhd.

[102] Sabade, S.S.; Walker, D.M.H.; "Comparison of Effectiveness of Current Ratio and Delta-I<sub>DDO</sub> Tests", Proceedings. 17<sup>th</sup> International Conference on VLSI Design, 2004.

[103] FA flow for BCD technology devices (Structural Failure) – Automotive

[104] Franco Stellari, Peilin Song, James C. Tsang, Moyra K. McManus and Mark

B. Ketchen : "Testing and Diagnostics of CMOS Circuits Using Light Testing of the second from Off-State Leakage Current", IEEE Transactions On Electron Devices, vol. 51, no. 9, September 2004.

[105] Khine Nyunt: "Photon Emission Microscope as an Inspection Tool for Semiconductor Device Reliability Analysis and Failure Diagnostics", Invited Paper: 1<sup>st</sup> National Colloquium on Photonics NPC2005, 29-30 November 2005, ESSET, Kajang, Selangor, Malaysia.'

[106] S. Yellampalli and A. Srivastava: "ΔI<sub>DDQ</sub> Testing of CMOS Data Converters", Proc. of the 49th IEEE International Midwest Symposium on Circuits and Systems (MWSCAS2006), Aug. 6-9, 2006, San Juan, Puerto Rico, U.S.A.

[107] Piet Engelke, Ilia Polian1 Hans Manhaeve, Michel Renovell, Bernd Becker: "Delta-I<sub>DDO</sub> Testing of Resistive Short Defects", Test Symposium, 2006. ATS '06. 15th Asian

[108] Silke Liebert: "Failure Analysis from the Back Side of a Die", Conference Proceedings of the 26th International Symuosium for Testina and Failure Analysis; pages 177-185

[109] Failure Analysis equipments – Automotive Product Group (APG), ST Microelectronics Sdn Bhd Muar.

[110] Die Processing Analysis for BCD technology devices – Automotive Product Group (APG), ST Microelectronics Sdn Bhd.

[111] User Manual, Automatic Selected Area Polished (ASAP) – Radiant Ultra-Tech.

[112] S. K. Loh, Teo HT, S.P. Neo, Z.G. Song and C. K. Oh: "Application of Focus Ion Beam Circuit Edit in Failure Analysis", ICSE2006 Proc.2006, Kuala Lumpur, Malaysia.

[103] Siva G.Narendra and Anantha Chandrakasan : "Leakage in Nanoscale CMOS Technologies", Springer, 2005.

[104]Art Wager: "Wafer Probe Tests and Stresses Used for Quality and Reliability Improvement", 8th Annual KGD Workshop Napa, California September 2001.