## SIMULATION, FABRICATION AND CHARACTERIZATION OF PMOS TRANSISTOR DEVICE

SITI IDZUPA SENTI YUSUF

MOLEJ UNIVERSITI TEKNOLOGI TUR HUSSEIN ONN

#### KOLEJ UNIVERSITI TEKNOLOGI TUN HUSSEIN ONN

#### PENGESAHAN STATUS LAPORAN PROJEK SARJANA

TITLE: SIMULATION, FABRICATION AND CHARACTERIZATION OF PMOS TRANSISTOR DEVICE

SESI PENGAJIAN: 2006/2007

Saya SITI IDZURA BINTI YUSUF mengaku membenarkan Laporan Projek Sarjana ini disimpan di Perpustakaan dengan syarat-syarat kegunaan seperti berikut:

- 1. Laporan Projek Sarjana adalah hakmilik Kolej Universiti Teknologi Tun Hussein Onn.

- 2. Perpustakaan dibenarkan membuat salinan untuk tujuan pengajian sahaja.

- 3. Perpustakaan dibenarkan membuat salinan tesis ini sebagai bahan pertukaran antara institusi pengajian tinggi.

- 4. \*\* Sila tandakan (√)

| SULI | I |

|------|---|

(Mengandungi maklumat yang berdarjah keselamatan atau kepentingan Malaysia seperti yang termaktub di dalam AKTA RAHSIA RASMI 1972)

TERHAD

(Mengandungi maklumat TERHAD yang telah ditentukan oleh organisasi/badan di mana penyelidikan dijalankan

TIDAK TERHAD

Disahkan oleh

(TANDATANGAN PENULIS)

(TANDATANGAN PENYELIA)

Alamat Tetap:

PEJABAT LADANG FELDA LEPAR UTARA 13, WAKIL POS LEPAR UTARA 1, 84300 BANDAR PUSAT JENGKA, **PAHANG**

Tarikh:

21 DISEMBER 2006

PROF. Dr. HASHIM BIN SAIM

Nama Penyelia

Tarikh:

21 DISEMBER 2006

CATATAN:

Jika Laporan Projek Sarjana ini SULIT atau TERHAD, sila lampirkan surat daripada pihak berkuasa/organisasi berkenaan dengan menyatakan sekali sebab dan tempoh laporan ini perlu di kelaskan sebagai SULIT atau TERHAD.

"I hereby declare that I have read this thesis and in my opinion this thesis in terms of content and quality requirement fulfills the purpose for the award of the Master of Electrical Engineering"

Signature

Name of Supervisor : PROFESSOR Dr. HASHIM BIN SAIM

Date : 21 DECEMBER 2006

## SIMULATION, FABRICATION AND CHARACTERIZATION OF PMOS TRANSISTOR DEVICE

#### SITI IDZURA BINTI YUSUF

Faculty of Electrical And Electronic Engineering

Tun Hussien Onn University College of Technology

"I hereby declare that the work in this thesis in my own except for quotations and summaries which have been duly acknowledged"

Signature

TUNKU TUN AMINAH : SITI IDZURA BINTI YUSUF Name of Student

: 21 DECEMBER 2006 PERPUSTAKAAN Date

Khas buat tunang Muhammad Syukur Bin Ismail

Setiap kejayaanku milik kita bersama

#### **ACKNOWLEDGEMENTS**

I would like to express my deep gratitude especially to my project supervisor, Prof. Dr. Hashim B. Saim for the oppurtunity and encouragement given throughout the entire process of my project. Iam deeply indebted for his advices and by providing the laboratory facility to me along the way.

Beside that, my special thanks to my father Yusuf B Hamdan, my mother Zainon Bt Kasran and my siblings who have always behind me to support during critical time. You are always in my heart.

Not forgeting, to all my Sarjana MEE members who have helped me along the way. Thank you for the suggestions and encouragements.

#### **ABSTRACT**

In a low supply voltage CMOS technology, it is desirable to scale threshold voltage and gate length for improving circuit performance. Therefore, a project has been carried out inside KUiTTHO's microelectronic cleanroom to produce a method that has better low power/low voltage current concentrate on p-channel (PMOS). An experiment was also done to determine the right parameter value to be used for fabrication process such as oxidation process thickness rate, sheet resistance and metal thickness. From the produced. Fabrication simulation was performed to produce a 0.1 µm and 0.3 µm PMOS transistor by using the ISE TOAR. parameter value obtained, 0.3 mm and 0.5 mm PMOS transistor had been successfully transistor by using the ISE-TCAD software. The trade off between threshold voltage (V<sub>TH</sub>), gate length (L<sub>G</sub>) and thin oxide thickness (t<sub>ox</sub>) are discussed to determine the characteristics of the transistors. It shows that for 0.3 mm ( $t_{ox} = 860 \text{Å}$ ) PMOS transistor the value of  $V_{TH}$  =-3.33V and 0.5 mm ( $t_{ox}$  = 910Å),  $V_{TH}$  value =-4.3V. From the simulation result show for  $0.1 \mu m$  ( $t_{ox} = 200 \text{Å}$ ),  $V_{TH} = -0.314 \text{V}$  and for  $0.5 \mu m$  (400 Å)  $V_{TH} = -0.634V$ . The result shows that, with decreasing gate length and oxide thickness will produce lower value of threshold voltage. Minimum value of threshold voltage can result in a better performance of transistor. Another parameter must be taken into consideration such as leakage current, resistivity and conductivity to get a better design of PMOS transistor in future research.

#### **ABSTRAK**

Untuk menghasilkan sumber voltan yang rendah dalam CMOS teknologi, penskalaan voltan ambang, V<sub>TH</sub> dan lebar gate, L<sub>G</sub> untuk menghasilkan litar yang berkeupayaan tinggi ,merupakan isue yang sangat penting. Oleh itu, projek ini telah dijalankan di dalam makmal mikroelektronik bilik bersih KUiTTHO untuk menghasilkan resepi bagi PMOS transistor dengan saiz yang minimum dan berprestasi tinggi. Eksperimen juga telah dijalankan untuk menentukan nilai parameter yang sesuai untuk digunakan dalam proses fabrikasi iaitu proses pengoksidaan untuk mencari kadar ketebalan oksida get, rintangan keping dan ketebalan metal. Daripada nilai parameter yang diperolehi, 0.3mm dan 0.5mm PMOS transistor telah berjaya dihasilkan. Fabrikasi secara simulasi juga telah dijalankan untuk menghasilkan 0.1 µm and 0.3 µm PMOS transistor dengan menggunakan perisian ISE-TCAD. Perubahan antara voltan ambang (V<sub>TH</sub>), lebar gate (L<sub>G</sub>) dan ketebalan lapisan oksida (t<sub>ox</sub>) telah dibincangkan untuk menetukan ciri-ciri bagi PMOS transistor tersebut. Hasil dapat daripada fabrikasi sebenar menunjukkan untuk transistor bersaiz 0.3mm (t<sub>ox</sub>= 860Å) PMOS transistor  $V_{TH} = -3.33 \text{V}$  dan  $0.5 \text{mm}(t_{ox} = 910 \text{ Å})$ , nilai  $V_{TH} = -4.3 \text{V}$ . Dapatan hasil simulasi menunjukkan untuk  $0.1 \mu m$  ( $t_{ox} = 200 \text{Å}$ ),  $V_{TH} = -0.314 \text{V}$  dan  $0.5 \mu m$  ( $t_{ox} = 400 \text{Å}$ ), nilai V<sub>TH</sub> = -0.634V. Daripada keputusan yang diperolehi menunjukkan bahawa dengan kelebaran get yang minima dan ketebalan oksida yang lebih nipis akan menghasilkan PMOS transistor dengan nilai voltan ambang yang lebih rendah. Nilai voltan ambang yang lebih rendah akan mempengaruhi keupayaan transistor. Parameter-parameter lain perlu diambil kira seperti arus bocor, kerintangan dan kekonduksian untuk menghasilkan PMOS transistor yang berprestasi tinggi untuk kajian akan datang.

3

3

4

#### TABLE OF CONTENT

| CHAPTER        | TITLE                                                                                                                                  | PAGE                            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| PERPL<br>PERPL | DECLARATION DEDICATION ACKNOWLEDGEMENT ABSTRACT ABSTRAK TABLE OF CONTENT LIST OF FIGURES LIST OF TABLES LIST OF SYMBOLS / ABBREVIATION | ii iii iv v vi vii xi xiii xiiv |

| CHAPTER I      | INTRODUCTION                                                                                                                           |                                 |

|                | 1.1 General                                                                                                                            | 1                               |

|                | 1.2 Problem Statement                                                                                                                  | 2                               |

Project Objectives

Project Scope

Project Flow

1.3

1.4

27

2728

| CHAPTER II | LITE | RATUI  | RE REVIEW                             |         |

|------------|------|--------|---------------------------------------|---------|

|            | 2.1  | Introd | uction                                | 5       |

|            | 2.2  | The M  | IOS Transistor                        | 5       |

|            | 2.3  | P-Cha  | nnel MOSFET (PMOS)                    | 6       |

|            |      | 2.3.1  | Structure of P-Channel MOS (PMOS)     | •       |

|            |      | Transi | stor                                  | 6       |

|            | 2.4  | Qualit | atitive I-V Behavior of PMOS          | 7       |

|            |      | Transi | stor                                  |         |

|            | 2.5  | Chara  | cteristics of the PMOS Transistor     | 9       |

|            | 2.6  | Relati | onship between Gate Length, Threshold |         |

|            |      | Voltag | ge and Gate Oxide Thickness           | 13      |

|            |      | 2.6.1  | Gate Length                           | 13      |

|            |      | 2.6.2  | Gate Oxide Thickness                  | 14      |

| . ot       |      | 2.6.3  | Threshold Voltage                     | 15      |

|            | 2.7  | Fabric | ation Process                         | 15AMINA |

|            |      | 2.7.1  | Cleanroom Cleanliness                 | 16      |

|            | -    | 2.7.2  | Cleaning Process                      | 17      |

| PERPU      | 51   | 2.7.3  | Oxidation Process                     | 18      |

| PLK        |      |        | 2.7.3.1 Horizontal Tube Furnace       | 19      |

|            |      |        | 2.7.3.2 Dry Oxygen                    | 20      |

|            |      |        | 2.7.3.3 Water Vapor Source            | 21      |

|            |      | 2.7.4  | Diffusion                             | 22      |

|            |      | 2.7.5  | Photolithography                      | 23      |

|            |      | 2.7.6  | Metallization                         | 24      |

|            | 2.8  | Simula | ation Fabrication Process             | 25      |

|            |      | 2.8.1  | Strongly Varying Length Scale         | 26      |

2.8.2 High Performance in Key Operations

2.8.3 Stability

Previous Research

71

72

#### **METHODOLOGY CHAPTER III** 30 3.1 Introduction Mask Design and Creation 31 3.2 Fabrication Process Module 33 3.3 Drain and source regions 33 3.3.1 3.3.2 Gate Oxide Grown 35 3.3.3 Define Contact Hole 36 3.3.4 Aluminium Film Deposited 37 3.4 PMOS Characteristics and Performance 38 Simulation Fabrication Process 38 3.5 RESULTS AND DISCUSSION **CHAPTER IV** Introduction 4.1 Recipes of PMOSFET Devices 4.2 4.2.1 Process Parameter 41 4.2.1.1 Oxidation Process 41 4.2.1.2 Diffusion 45 45 4.2.1.2.1 Sheet Resistance 48 4.2.1.3 Metallization Sheet Resistance 51 4.2.2 Fabrication Process 57 4.3 PMOS Characteristics Analysis Simulation Fabrication Result 58 4.3.1.1 Conclusion 64 65

4.3.2 Real Fabrication Result

PMOS Characteristics and Performance

4.3.3 Conclusion

#### CHAPTER V CONCLUSION AND RECOMMENDATION

| 5.1 | Introd                      | uction                               | 74 |  |  |

|-----|-----------------------------|--------------------------------------|----|--|--|

| 5.2 | Concl                       | Conclusion                           |    |  |  |

| 5.3 | Problems and Recommendation |                                      |    |  |  |

|     | 5.3.1                       | Uniformity in Diffusion Process      | 77 |  |  |

|     | 5.3.2                       | Measurement of V <sub>TH</sub> Value | 77 |  |  |

|     | 5.3.3                       | Alignment                            | 77 |  |  |

| 5.4 | Sugge                       | stion for Future Research            | 78 |  |  |

#### LIST OF FIGURES

|   | FIGURE NO | . TITLE                                              | PAGE |

|---|-----------|------------------------------------------------------|------|

|   |           |                                                      |      |

|   | 1.1       | The project flowchart                                | 4    |

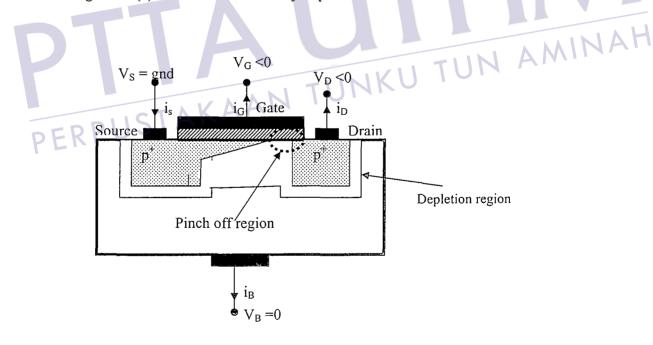

|   | 2.1       | An internal structure of p-channel MOS transistor    | 7    |

|   | 2.2       | Cross section of an enhancement-mode PMOS transistor | 8    |

| 1 | 2.3(a)    | $V_{SG} \le V_{TH} - \text{cut off region}$          | 10   |

|   | 2.3(b)    | $V_{SG} \ge V_{TH} - linear region$                  | 10   |

|   | 2.3(c)    | PMOS with channel just pinch off at the drain        | 11   |

|   | 2.3(d)    | Pinch off for $V_{SD} \ge (V_{SG} + V_{TH}) \ge 0$   | 11   |

|   | 2.4 PER   | Class 100 yellow room for photolithography process   | 16   |

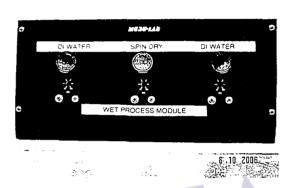

|   | 2.5(a)    | Cleaning Process Section                             | 18   |

|   | 2.5(b)    | D.I water                                            | 18   |

|   | 2.6       | Furnace Equipment                                    | 20   |

|   | 2.7       | Bubler water vapor source                            | 21   |

|   | 2.8(a)    | Spin on-dopant Equipment                             | 24   |

|   | 2.8(b)    | Transfer Patern Equipment                            | 24   |

|   | 2.9       | Physical Vapor Deposition(PVD) Equipment             | 25   |

|   | 2.10      | ISE TCAD product overview                            | 27   |

|   | 3.1       | PMOS transistor layout                               | 31   |

|   | 3.2       | Masking drawing steps in TurboCAD 2002               | 32   |

|   | 3.3       | Modules of MOSFET PMOS fabrication process           | 33   |

|   | 3 4       | Gate Oxide Grown                                     | 35   |

| 3.5        | Define Contact Hole                                                           | 36 |

|------------|-------------------------------------------------------------------------------|----|

| 3.6        | Completion of PMOS transistor fabrication                                     | 37 |

| 4.1        | Oxidation thickness versus time for wet oxidation                             | 43 |

| 4.2        | Oxidation thickness versus time for dry oxidation                             | 44 |

| 4.3        | Five Point of measurement                                                     | 44 |

| 4.4(a)     | Example of sheet resistance graph measured by four                            |    |

|            | point probe for wafer A at point 1                                            | 47 |

| 4.4(b)     | Example of sheet resistance graph measured by four point                      |    |

|            | probe for wafer B (b) at point 1                                              | 47 |

| 4.5        | Graph Aluminium thickness with different size of aluminium                    | 50 |

| 4.6(a)     | $I_D$ - $V_D$ characteristics of 0.1um PMOS, thin oxide 400Å                  | 58 |

| 4.6(b)     | Transfer charateristics of 0.1 µm PMOS, thin oxide 400Å                       | 59 |

| 4.7(a)     | I <sub>D</sub> -V <sub>D</sub> characteristics of 0.3um PMOS, thin oxide 400Å | 60 |

| 4.7(b)     | Transfer charateristics of 0.3 µm PMOS, thin oxide 400Å                       | 60 |

| 4.8(a)     | I <sub>D</sub> -V <sub>D</sub> characteristics of 0.1um PMOS, thin oxide 200Å | 62 |

| 4.8(b)     | Transfer charateristics of 0.1 µm PMOS, thin oxide 200Å                       | 62 |

| 4.9(a)     | I <sub>D</sub> -V <sub>D</sub> characteristics of 0.3um PMOS, thin oxide 200Å | 63 |

| 4.9(b)     | Transfer charateristics of 0.3 µm PMOS, thin oxide 200Å                       | 64 |

| 4.10 P E R | $I_D$ - $V_D$ characteristics of 0.3 mm PMOS; $V_D$ =-6V;                     |    |

|            | thin oxide 910Å                                                               | 66 |

| 4.11       | $I_D$ - $V_D$ characteristics of 0.5 mm PMOS; $V_D$ =-6V;                     |    |

|            | thin oxide 910Å                                                               | 67 |

| 4.12       | $I_D$ - $V_D$ characteristics of 0.3 mm PMOS; $V_D$ =-6V;                     |    |

|            | thin oxide 860Å                                                               | 69 |

| 4.13       | $I_D$ - $V_D$ characteristics of 0.5 mm PMOS; $V_D$ =-6V;                     |    |

|            | thin oxide 860Å                                                               | 69 |

#### LIST OF TABLES

| NO. TABLE | TITLE                                              | PAGE      |

|-----------|----------------------------------------------------|-----------|

|           |                                                    |           |

| 2.1       | Cleanroom cleanliness measurement                  | 17        |

| 3.1       | Modules of MOSFET (PMOSS) fabrication process      | 33        |

| 3.2       | Equipment of device and process parameter          | 38        |

| 4.1(a)    | Wet oxidation thickness of wafer 1                 | 42        |

| 4.1(b)    | Wet oxidation thickness of wafer 2                 | N42 A M I |

| 4.2       | Oxidation thickness for dry oxidation 43           |           |

| 4.3       | Sheet resistance value different wafer             | 46        |

| 4.4 PE    | Metal thickness with different size of aluminium   | 50        |

| 4.5       | The recipes of PMOS transistor                     | 51        |

| 4.6       | Simulation fabrication result                      | 65        |

| 4.7       | Real fabrication result                            | 70        |

| 4.8       | Relationship between different gate oxide and gate |           |

|           | length versus gate delay                           | 73        |

| 4.9       | Gate delay with load capacitance                   | 73        |

xiv

#### LIST OF SYMBOLS / ABBREVATIONS

symbol for  $10^{-10}$ cm or  $10^{-8}$ m Å

C Capacitance

Oxide capacitance per unit area  $C_{ox}$

Diffusion coefficient D

Ι Current

Drain current  $I_D$

SAAN TUNKU TUN AMINAH Drain Current versus Drain / source Voltage  $I_D$ - $V_D$

k Boltzmann's constant

L Length

Gate Length  $L_{G}$

PEK Electron density n

Intrinsic carrier density  $n_i$

N Doping density

$N_a$ Acceptor doping density

$N_c$ Effective density of states in the conduction band

$N_{d}$ Donor doping density

R Resistance

Sheet Resistance  $R_{\mathsf{s}}$

$S_{i}$ Silicon

Thickness t

Oxide thickness  $t_{ox}$

T Temperature

Velocity

V<sub>D</sub> Drain voltage

$V_{DS}$  Voltage gate to source

V<sub>B</sub> Body voltage

V<sub>G</sub> Gate voltage

V<sub>GS</sub> Voltage gate to source

$V_{TH}$  Threshold voltage

W Width

$x_{d}$  Depletion layer width

xj Junction depth

$x_n$  Depletion layer width in an n-type semiconductor

$\mu_p \qquad \qquad \text{Hole mobility}$

#### **CHAPTER I**

#### INTRODUCTION

AMINA

#### 1.1 General

The MOSFET circuit technology has dramatically changed over the last three decades. Starting with a ten-micron PMOS process with an aluminum gate and a single metallization layer around 1970, the technology has evolved into a tenth-micron self-aligned-gate CMOS process with up to five metallization levels. The transition from dopant diffusion to ion implantation, from thermal oxidation to oxide deposition, from a metal gate to a poly-silicon gate, from wet chemical etching to dry etching and more recently from aluminum (with 2% copper) wiring to copper wiring has provided vastly superior analog and digital CMOS circuits. The choice and centering of target transistor parameters- modeling (such as threshold voltage, gate length, gate oxide thickness, etc) for high speed low-power/ low voltage CMOS technologies is a current concern (Chang, 2000)[7]. If proper CMOS scaling rules are utilized, high speed CMOS technologies can be achieved even in conjunction with reduced supply voltage requirements. The dynamic power dissipation in CMOS inverter circuits is given by

$$P = f. C_L. V_D^2$$

(1.1)

where f is operating frequency,  $C_L$  is the loading capacitance, and  $V_D$  is the supply voltage. Clearly, reducing the supply voltage is the simplest approach in reducing the dynamic power consumption. The time delay,  $\tau_D$  in a CMOS gate is approximately given by

$$\tau_D \approx \frac{C_L V_D}{I_D} \propto \frac{C_L L_G t_{ox} V_D}{(V_D - V_{TH})^2}$$

(1.2)

where L<sub>G</sub> is the transistor gate length, t<sub>ox</sub> is the gate oxide thickness, I<sub>D</sub> drain current and V<sub>TH</sub> is the MOS transistor threshold voltage. Equation 1.2 demonstrates the need for reducing the gate oxide thickness, the gate length, and the transistor threshold voltage in order to preserve the high-speed in a reduced voltage supply technology.

#### 1.2 Problem Statement

Since the semiconductor industry growth rapidly, competition among companies to fulfill market demands has become increasingly intense. Therefore, many data and parameters obtained from researches were not published and kept confidential. Hence, each fabrication laboratories have created their own technologies. KUiTTHO as an education institution is also making an effort to produce a MOSFET technology transistor with the equipment provided in the KUiTTHO's Microelectronic Cleanroom. Therefore, the purpose of this project was to build a first MOSFET technology transistor, which was aimed for better low power/low voltage current concentrate on p-channel (PMOS) transistors.

#### 1.3 Project Objectives

The objectives of this project are:

- 1. To produce a recipe of MOSFET devices (PMOS transistor).

- 2. To determine the minimum mask design that can be fabricated in KUiTTHO's cleanroom to produce transistor with minimum gate length.

- 3. To determine transistor region operation which are very important in low-voltage and low-power application from the IV characteristics of PMOS transistor.

- 4. To determine the trade-off between threshold voltage (V<sub>TH</sub>) and the minimum gate length (L<sub>G</sub>) for optimizing the performance of PMOS transistors for low voltage/low power high-speed digital CMOS circuit.

#### 1.4 Project Scope

1. The project was done with the process equipments in Microeletronic Cleanroom at KUiTTHO. The data that was obtained might be different with other cleanroom. It depends on the equipment capability and the class of the cleanroom.

AKAAN TUNKU TUN AMINAH

- 2. The project concentrated on PMOS transistor device, including the effect of threshold voltage(V<sub>TH</sub>) thin oxide thickness (t<sub>ox</sub>) and gate length (L<sub>G</sub>) to I<sub>D</sub>-V<sub>D</sub> characteristics.

- 3. There were 4 steps that were taken in this project which were:

- Establishing process module, process parameters, process flow and process run card.

- ii. Optimizing and characterizing process module.

- iii. Integrating the process module and starting the fabrication process of MOSFET (PMOS) device.

- iv. Analyzing and testing product.

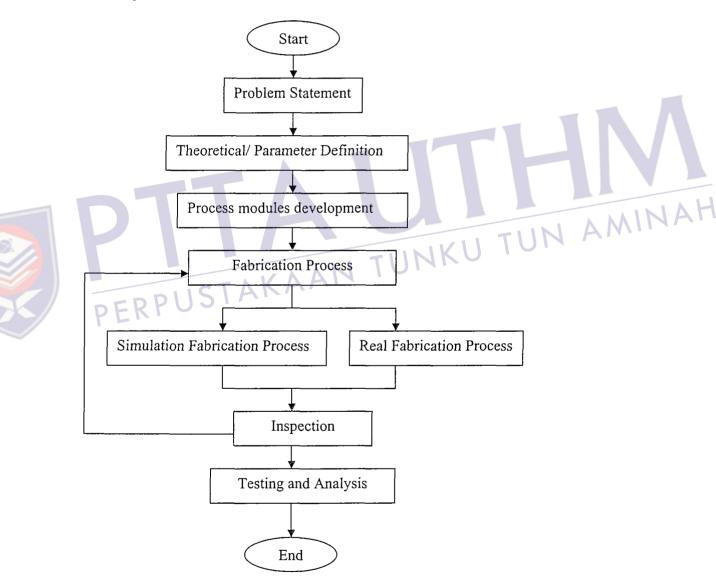

#### 1.5 Project Flow

Figure 1.1: The project flowchart

#### **CHAPTER II**

#### LITERATURE REVIEW

#### 2.1 Introduction

This chapter will highlight on the understanding of transistor device mainly MOSFET (Metal Oxide Semiconductor Field Effect Transistor). This project focuses on the fabrication process of MOSFET devices. Prior to that, the characteristics and physical structure of PMOS transistor was studied.

#### 2.2 The MOS Transistor

These devices are known as FET's (Field effect transistors), which consist of three regions; source, drain and gate. The resistance path between the drain and source is controlled by applying a voltage to the gate. This varies the depletion layer under the gate and thus reduces or increases the conductance path. The FET input impedance (unlike the BJT which is a few  $k\Omega$ ) is very high ( $\sim M\Omega$ 's) and as a result the gate current can be considered as zero.

#### 2.3 P-Channel MOSFET (PMOS)

A transistor is considered as depletion type if both source and drain are connected by a channel. This channel is created by implantation ion or diffusion process. If there are no channel exists, the operation of transistor known as depletion operation. The depletion mode used mainly in analog circuit. A p-channel depletion mode transistor, which can conceptually possible, has never been used in practical circuits.

In this project, the enhancement PMOS transistor will be used. It is relatively easy to make as an enhancement mode device, which is preferred choice for digital application since it minimizes the standard power dissipation.

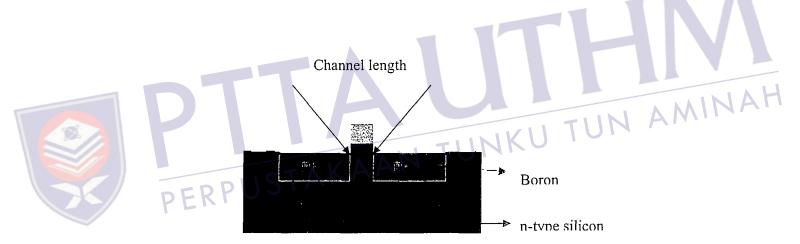

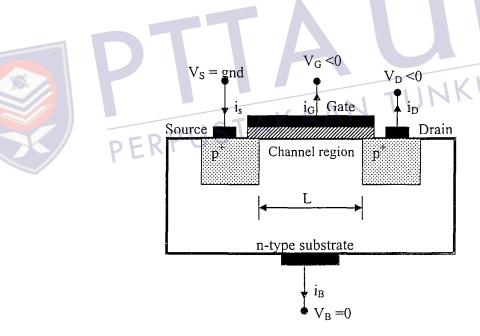

#### 2.3.1 Structure of P-Channel MOS (PMOS) Transistor

The transistor is formed on an n-type silicon body or substrate. Typical doping concentrations for the body are  $10^{14}$  to  $10^{18}$  cm<sup>-3</sup>. The dopant concentrations will be assumed uniform throughout the body. For p-channel MOS, typically the dopant material is Boron (Thomas,2000)[4]. The center part of the structure is covered by an insulator (typically silicon dioxide, which often referred to simply as oxide). The body interface to the oxide is often called the surface.

A low resistivity electrode, called the gate, is formed on the top oxide.

Contemporary processes commonly use polycrystalline silicon (polysilicon) for the gate.

In this case, metal was used instead of polysilicon. The two regions shown on the sides are formed by implanting or diffusing acceptor atoms, with the gate acting as a mask against the implant/diffused region. This mask receives the acceptor atoms itself and prevents them from landing under it (Douglas and Eshraghian, 1988)[1].

The region between the source and drain is called 'channel'. The channel width (W) and length (L) of individual transistors can vary greatly (from a fraction of micrometer to several hundred micrometer), depending on the circuit needs. In digital circuits, L is normally kept as the minimum value possible (Zant,2000)[12]. The internal structure of p-channel MOS transistor depicts in figure 2.1.

Figure 2.1: An internal structure of p-channel MOS transistor

#### 2.4 Qualitatitive I-V Behavior of PMOS Transistor

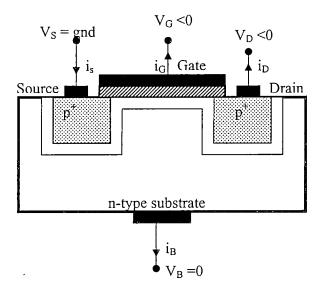

MOS transistor with p-type channel (PMOS) transistor easily be fabricated. In fact, the first commercial MOS transistor and integrated circuits used PMOS devices

because it was easier to control fabrication process of PMOS technology (Jaeger,1997) [14]. The enhancement mode PMOS device is fabricated by forming p-type source and drain regions in an n-type substrate as depicted in the device cross section in figure 2.2. By referring to the figure, the source, drain and body of the PMOSFET are all grounded.

In the figure 2.2, the condition shown are those for an unbiased device; however, the application of negative voltage of suitable magnitude ( $0 > V_{TH}$ ) between gate and source will give rise to the formation of a channel (p-type) between the source and drain and current may then flow if the drain is made negative with respect to the source. In this case the current is carried by holes as opposed to electrons (as in the case for nmos device). In consequence, PMOS transistors are inherently slower than NMOS, since hole mobility  $\mu_p$  is less by a factor of 2.5 apporoximately than electron mobility  $\mu_p$ .

Figure 2.2: Cross section of an enhancement-mode PMOS transistor

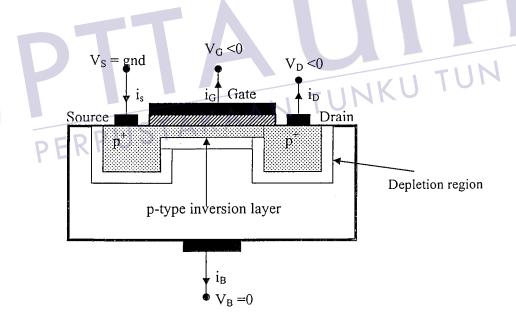

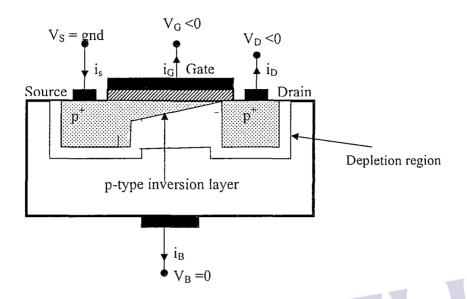

#### 2.5 Characteristics of the PMOS Transistor

Three sets of condition (cutoff region, linear region and saturating region) of enhance-mode PMOS transistor show as figure 2.3(a) through 2.3(d). In order to establish the channel in the first place a minimum voltage level of threshold voltage,  $V_{TH}$  must be established between gate and source and between gate and substrate. Figure 2.3(a) indicates the conditions prevailing with the channel established but no current flowing between source and drain ( $V_{SD} = 0$ ). The condition prevailing when current flows in the channel by applying a voltage  $V_{DS}$  between drain and source. It corresponding  $i_{SD}$  drop =  $V_{SD}$  along the channel.

This result in the voltage between gate and channel varying with distance along the channel with the voltage between gate and channel being a maximum og  $V_{SG}$  at the source end. Since the effective gate voltage is  $V_G = V_{SG} - V_{TH}$  (no current flows when  $V_{SG} \le -V_{TH}$ ) there will be voltage available to invert the channel at the drain. The limiting condition comes when  $V_{SD} = V_{SG} - V_{TH}$ . For all voltages  $V_{SG} + V_{TH} \ge V_{SD} \ge 0$ , the device is in the nonsaturated regoin of operation which is condition in figure 2.3(b).

When  $V_{SD}$  is increased to a level greather than  $V_{SG} - V_{TH}$ , in this case, an  $i_{SD} = V_{SG} - V_{TH}$  takes place over less than the whole length of the channel so that over part of the channel, near the drain, there is no electric field available to give rise to an inversion layer to create the channel. The channel is, therefore 'pinched off' as indicated in figure 2.3(c). Diffusion current completes the parh from source to drain in this case, causing the channel to exhibit a high resistance and behave as a constant current source. This region, known as saturation, is characterized by almost constant current for increase for  $V_{SD} \ge (V_{SG} + V_{TH}) \ge 0$ .

Figure 2.3(a) :  $V_{SG} \le V_{TH}$  – cut off region

Figure 2.3(b):  $V_{SG} \ge V_{TH} - linear region$

Figure 2.3(c): PMOS with channel just pinch off at the drain

Figure 2.3(d) : Pinch off for  $V_{SD} \ge (V_{SG} + V_{TH}) \ge 0$

TUN AMINAH

The mathematical model for the PMOS transistor is summarized in equation 2.1 through 2.3 for all region.

$$K_p = \mu_p C''_{ox} (W/L)$$

$i_G = 0$  and  $i_B = 0$

Cutoff region:

$$i_{SD} = 0$$

for  $V_{SG} \le -V_{TH}$  (2.1)

Linear region:

$$i_{SD} = K_p (V_{SG} + V_{TH} - (V_{SD}/2) V_{SD} \text{ for } V_{SG} + V_{TH} \ge V_{SD} \ge 0 (2.2)$$

Saturation region :

$$(V_{SG} + V_{TH})^2 (1 + \lambda V_{SD})$$

for  $V_{SD} \ge (V_{SG} + V_{TH}) \ge 0$  (2.3)

Where,

$K_p$  = transconductance parameters

C"<sub>ox</sub> = oxide capacitance per unit area (F/cm<sup>2</sup>)

W = channel width which is measured perpendicular to the direction of current

L = channel length which is measured in the direction of current in the channel

$\lambda$  = channel-length modulation parameter

$\mu_p$  = Hole mobility

$V_{SG}$  = source-gate voltage ; $V_{SD}$  = source-drain voltage;  $V_{TH}$  = the shold voltage

### 2.6 Relationship between Gate Length, Threshold Voltage and Gate Oxide Thickness

The length and width of a tarnsistor are the two most important dimensions of a transistor (Sami,(2004)[8]. When the people talk about the gate size of spesific technology, they are reffering to the minimum gate length. The critical dimensions that needs to be engineered are gate length( $L_G$ ), the gate oxide thickness ( $t_{ox}$ ), the depletion depths under the gate, the source-drain junction depth ( $x_j$ ) and steepness of the source-drain junction. All these quantities must be scaled together. In this project, the different of length gate ( $L_G$ ) and oxide thickness are take into consideration to determine the threshold voltage and performance of PMOS transistor.

# 2.6.1 Gate Length DERPIISTAKAAN TUNKU TUN AMINAH

Interm of layout design, the length of the transistoris the distance between the source and the drain of a transistor. This may not be intuitive, because the physical dimension of the transistor length is smaller than the width. In term of transistor performance, the length of the transistor is the distancesurable current flow. The gate voltage that controls the flow of current. If the distance between the source and drain is reduced, the gate voltage has a stronger influence in enabling current flow. More current conceptually means faster performance. Refer to the equation 1.1 (Chapter I)

$$\tau_D \approx \frac{C_L V_D}{I_D} \infty \frac{C_L L_G t_{ox} V_D}{\left(V_D - V_{TH}\right)^2}$$

it showed that the time delay  $\tau_D$ , proportional to the length gate,  $L_G$  and threshold voltage,  $V_{TH}$ . From the time delay, it can be determine the performance of the transistor.

The length of a transistor in terms of manufacturing capabilities is the narrowest possible piece of polysilicon (poly) that can be manufactured reliably. Smaller poly dimension and thus smaller transistor result in smaller ICs, so it is attractive to use the minimum gate length to minimize chip area [14]. However, these largely experimental techniques have never been proven in a manufacturing environment. The development of a reliable, manufacturable cost-effective lithography technique is absolutely essential to continued progress in CMOS technology.

#### 2.6.2 Gate Oxide Thickness

The electrical thickness of gate insulator must decrease with the channel length. Recently, studies of tunnelling through thickness oxide have shown that silicon dioxide can potentially be thinned to slightly below 2 nm before the leakage current and the associated dissipation become so large as to be unacceptable (Tsividis,1999)[17]. For equivalent electrical SiO<sub>2</sub> thickness below 2 nm, thicker gate insulators with a higher dielectric constant than silicon dioxide are being considerate to reduce the tunnelling current through the gate insulator.

AN TUNKU TUN AMINA

TUN AMINA

#### 2.6.3 Threshold Voltage

The gate structure of a MOS transistor consists, electrically, of charges store in the dielectric layers and in the surface interfaces as well as in the substrate itself. Switching an enhancement mode MOS transistor from the off to the on state consists of applying sufficient gate voltage to neutralize these charge and enable the underlying silicon to undergo an inversion due to the electric field from the gate. Increasing voltage source,  $V_{SB}$  causes the channel to be depleted of charge carriers and thus, the threshold voltage is raised. For the enhancement-mode PMOS transistor, threshold voltage,  $V_{TH}$  <0.

#### 2.7 Fabrication Process

The production of semiconductor is a challenging technological process. The success of operation management and production control technique is critically dependent upon the availability and performance of highly sophisticated and very expensive process equipment. Manufacturing semiconductors, also called integrated circuits or chips, requires repetitive sequences of similar processing operations such as oxidation, etch, photolithography, diffusion, ion implant and metallization.

#### 2.7.1 Cleanroom Cleanliness

The fabrication area consisted of a large room with the work station (called hoods) arranged in rows so that the wafers could move sequentially through the process, never being exposed to dirty air. Normal air is so laden with contaminants that it must be treated before entering a cleanroom. Air cleanliness levels in cleanrooms are identified by the particulate diameters and their density in the air. Air quality is designated by the *class number* of the air in the area as defined in Federal Standard209E (Ruska,1987)[18]. This standard designates air quality in the two categories of particle size and density. The class number of an area is defined as the number of particles 0.5µm or larger in a cubic foot of air. Advancing chip sensitivity has identified smaller and smaller tolerable particle sizes for each generation of chip feature size.

Federal Standard 209E defines class number at 0.5µm particle size, successful wafer fabrication processing requires tighter controls. With class number of 1000 contains maximum 0.5µm particles per cubic foot. In this project the work station fabrication process had been done in class 1000 room and photolithography process in class 100 yellow room (fig 2.4). The measurement of cleanliness of each room had been done and the result had been shown in table 2.1.

Figure 2.4: Class 100 yellow room for photolithography process

Table 2.1: Cleanroom cleanliness measurement

#### White Room – Class 1000

Area 1 - 54cm3

Area 2 – 111cm3

Area 3 – 38cm3

Area 4 – 64cm3

Total Particle – 267cm<sup>3</sup>

#### Yellow Room - Class 100

Area 1 - 17cm3

Area 2 - 19cm3

Area 3 - 15cm3

Total Particle – 51cm3

#### 2.7.2 Cleaning Process

To achieve high production yield and device reliability, it is essential to eliminate all sources of contamination. Surface cleaning is particularly important prior to high temperature process because impurities react and diffuse at much higher rates at elevated temperature. There are two types of cleaning process which are wet cleaning and dry cleaning. In this project the wet cleaning will be used. Chemical cleaning is standard for the wafer clean, using solvent asid such as Buffered Oxide Etching (BOE) to remove organic and inorganic contaminants residue, respectively. It is usually followed by deionized (DI) water rinse and spin dry process.

Most common process used is the RCA wet cleaning process. RCA cleaning process is the composition of  $NH_4OH-H_2O_2-H_2O$  (1:1:5 – 1:1:7 at  $70^{\circ}C$  to  $80^{\circ}C$ ). This composition can effectively remove organic contamination and particle by oxidation. It also can be used for complete fulfillment of an ultra clean wafer surface; it should be free from particle, organic contamination, metal contamination, surface microroughness & native oxide. Figure 2.5(a) and 2.5(b) shows clean process equipment.

The RCA formulas have been proven durable over the years, and are still the base cleaning process for most pre-furnace cleaning. Improvements in chemical purity have kept pace with industry cleaning needs. These solutions have been found to be as effective as the more concentrated versions. Additionally, they produce less micro roughing and are cost effective and easier to remove.

Figure 2.5(a): Cleaning Process Section

Figure 2.5(b) D.I water

Oxidation is one of the most important thermal processes. It is an adding process, which adds oxygen to a silicon wafer to form silicon dioxide to a silicon surface [8]. The oxidation rate controlled by four conditions:

- i. Temperature

- ii. Pressure

- iii. Time

- iv. Crystal orientation

The oxidation process can be carried out through wet or dry conditions in this project. The process will be done by furnace with horizontal reactor. Dry oxidation simply flow oxygen gas over the silicon and reaction that occurs is:

$$Si + O_2 \longrightarrow SiO_2$$

(2.5)

Wet condition produced the fastest reaction rate. Wet condition can be developed by flowing oxygen through wafer so the oxygen carries it with water vapor. The reaction that occurs is:

$$Si + 2H_2O \longrightarrow SiO_2 + 2H_2$$

(2.6)

#### 2.7.3.1 Horizontal Tube Furnace

Horizontal tube furnaces have been used in the industry since the early 1960s for oxidation, diffusion, heat treating and various deposition processes. They were first developed for diffusion processes in germanium technology and to this day are often call diffusion furnaces or tube furnace. Horizontal designs evolved into vertical designs with a number of advantages.

Basic single horizontal three-zone tube furnace is shown in fig 2.6. It consists of a long ceramics tube, with coils of copper tubing on the inside furnace. Each of the coiled tubes defines a zone and is connected to separate power supply operated by a proportional band controller. Furnace may have up to seven separate zones. Inside the furnace tube is quartz reaction tube that serves as the reaction chamber for the oxidation or other processes. The reaction tube may itself be inside a ceramic liner called a muffle. The muffle acts as a heat sink fostering a more even heat distribution along the quartz tube.

Thermocouples are positioned against the quartz tube and send temperature information to the proportional band controllers. The controllers proportion power to the coils, which in turn heat the reaction tube by radiation and conduction. Radiation heating comes from the energy given off by the coil and impinging on the tube. Conduction takes place where the coils touch the tube. These controllers are very sophisticated and can control temperatures in the center zone to plus or minus 0.5°.

#### 2.7.3.2 Dry Oxygen

When oxygen is used as the oxidant, it is supplied from the facility source or from tanks of compressed oxygen located in the source cabinet. It is imperative that the gas be dry; that is, not contaminated with water vapor. The presence of water vapor in the oxygen would increase the oxidation rate and cause the oxide layer to be out of specification. Dry oxygen oxidation is the preferred method for growing the very thin (<1000 angstroms, Å) gate oxides required for MOS devices.

UN AMINAH

#### 2.7.3.3 Water Vapor Source

There are several methods used to supply water vapor (steam) into the oxidation tube. In this project Bubbler water vapor source is used to growth oxide layer onto silicon wafer during steam or wet oxidation process. For oxidation, the bubbler liquid is deionized (D.I. water) (Fig 2.7) heated close to the boiling point (98 to 99°C), which creates a water vapor in the space above the liquid. As the carrier gas is bubbled through the water and passes through the vapor, it becomes saturated with water. Under the influence of the elevated temperature inside the tube, the water vapor becomes steam and causes the oxidation of the silicon surface. With bubblers technique, there is always concern about contamination potential is heightened by the need to open the system periodically to replenish the water.

Figure 2.7: Bubler water vapor source

#### 2.7.4 Diffusion

Diffusion has historically been the most important processing steps used in the fabrication of monolithic integrated circuits. For many years, diffusion was the primary method of introducing impurities such as Boron, Phosphorous, and antimony into silicon to control majority-carries type and resistivity of layer formed in the wafer. Because of the most commonly used tool for silicon doping was the high-temperature quartz tube furnace, it has been called the 'diffusion furnace' ever since in figure 2.6.

The commonly used diffusion doping process sequence is predeposition, then drive-in. At a first layer of dopant oxide, B<sub>2</sub>O<sub>3</sub> is deposited on the wafer surface at high temperature, followed by thermal oxidation process that consumes the residue dopant gas and grows the layer of silicon dioxide, which caps the dopant and prevent out-diffusion.

Boron: Predeposition:

$$B_2H_6 + 2O_2 \longrightarrow B_2O_3 + 3H_2O$$

(2.7)

Drive-in :

$$2B_2O_3 + 3Si \longrightarrow 4B + 3SiO_2$$

(2.8)

#### 2.7.5 Photolithography

Photolitogrphy is the core of the ICs manufacturing process. Photolithography is the patterning process that transfers the design pattern from the mask or reticle to the photoresist on the wafer surface. Photolithography was first used in the printing industry and has long been used to make printed circuit board. It was adapted in semiconductor industry for transistor and integrated circuit in the 1950s.

Photolithography is one of the most critical operations in semiconductor processing. It is the process that sets the surface dimensions on the various parts of the device and circuits. The goal of the operation is twofold. First, is to create in and on the wafer surface pattern whose dimensions are as close to the design requirement as possible. This goal is referred to as the resolution of the images on the wafer. The pattern dimensions are referred to as the feature sizes or image size of the circuit.

The second goal is the correct placement (called alignment or registration) of the circuit pattern on the wafer. The entire circuit pattern must be correctly placed on the wafer surface and the individual parts of the circuit must be in the correct position relative to each other. In a circuit, the effects of misalignment mask layers can cause the entire circuit to fail.

The photolithography process includes three major steps; photoresist coating, alignment and exposure and photoresist developing. To achieve high resolution, photolithography also has soft bake and chilling process. After developing process, the wafer through patterned inspection process and if a wafer failed to pass the inspection, it by passed the hard bake steps, the photoresist stripped, and whole process repeated until it passed the inspection (Jacob and Harry, 1998)[13], (fig 2.8(a) and 2.8(b)). The selection

of a resist and development of resist process is a detail and lengthy procedure. Once a resist process is established, it is changed very reluctantly. In this project, photolithography process had been done in a room class 100 and named as yellow room.

Figure 2.8(a): Spin on-dopant Equipment Figure 2.8(b): Transfer Patern Equipment

KAAN TUNKU TUN AMINAH

#### 2.7.6 Metallization

A variety of conductors is applied in IC chip manufacturing. Metals with high conductivity are widely used for interconnections forming microelectronics circuits. Metallization is an adding process that deposits metal layers on the wafer surface. Metal such as copper and aluminum are good conductors, widely used to make conducting lines to transport electrical power signals. In this project, the metal used was aluminum and the process will be done by PVD equipment.

Sputter deposition (sputtering) is a process adapted to semiconductor needs. Sputtering is a process that can deposit any material on any substrate. It is widely used

#### REFERENCES

- [1] A. P Douglas and K. Eshraghian (1988). *Basic VLSI Design System and Circuit*. Prentice-Hall of India

- [2] B. Goncal, H. Marton and P. Carles (2001). A High Performance 0.18um CMOS technology Designed for Manufacturability. IEEE Electron Device Letters. Vol.8, No.7. Nov 2001.

- [3] C. Kizilyalli and S.A Lytle (1995). Threshold Voltage-minimum Gate Length

Trade-off in Buried channel PMOS Devices for Scaled Supply Voltage CMOS

Technologies. IEEE Electron Device Letters. Vol.16, No.10. October 1995.

- [4] C.M Thomas (2000). *CMOS IC Layout*. First Edition. Butterworth-Heinemann Publisher.

- [5] C. Robert, K. Jack., R. Brian and D. Lionberger (2000). 30nm Physical Gate Length CMOS Transistor with 1.0 ps n-MOS and 1.7 ps p-MOS Gate Delay. Component Research, Logic technology Development, Intel Corporation, Hillsborough

- [6] C.Y Chang and S.M Sze (1996). ULSI Technology. The McGraw-Hill Companies

- [7] C.Y Chang (2000). ULSI Device. John Wiley & Sons, Inc

- [8] F. Sami (2004). Introduction to Microfabrication. First Edition. John Wiley & Sons Ltd

- [9] K. Andrew, M. Swamy(2006). *Impact of Gate-Length Biasing on Threshold-Voltage Selection*. 7th International Symposium on Quality Electronic Design (ISQED'06). pp. 747-754.

- [10] M. S Kang and Y. Leblebici (2003). CMOS Digital Integrated Circuits. Third Edition. Mc Graw Hill

- [11] O. Michael and M. Linda (2000). Impact of Spatial Intrachip Gate Length

Variability on the Performance of High Speed Digital Circuit. IEEE Transactions

on Computer Aided Design of Integrated Circuits and System. Vol 21. No 5.

May 2002

- [12] P.V Zant (2000) . Microchip Fabrication A Practical Guide to Semiconductor Processing. McGraw-Hill. Fourth Edition.

- [13] R. Jacob and W. Harry (1998). CMOS Circuit Design, Layout and Simulation. A John Wiley & Sons, INC., Publication.

- [14] R.C Jaeger (1997). Microelectronic Circuit Design. The McGraw-Hill Companies, Inc

- [15] S.Y. Kiat, Samir S. Rofail (2002). CMOS/BiCMOS ULSI Low Voltage, Low Power. Prentice Hall Modern Semiconductor Design Series.

- [16] T. Ghani, S. Ahmed, P. Aminzadeh\*, J. Bielefeld, P. Charvat, C. Chu, M. Harper and P. Jacob, C. (2000). 100 nm Gate Length High Performance / Low Power CMOS Transistor Structure. Component Research, Logic technology Development, Intel Corporation, Hillsborough

- [17] Tsividis, Yannis (1999). Operation and Modeling the MOS Transistor. Second Edition, McGraw-Hill.

- [18] W. Scot Ruska (1987). Microelectronic Processing an Introduction to the Manufacture of Integrated Circuit. McGraw-Hill International Edition

- [19] W.K. Suk, Y.D Kim and H. J Young(2004). Frequency characteristics of sub-100 nm double-gate MOSFET for suppressing short channel effects. Semicond. Sci. Technol.. No.4

- [20] Y. Bin, H. Wang, and M.R Lin (2001). Scaling Towards 35nm Gate Length CMOS Scaling Towards 35nm Gate Length CMOS. Symposium on VLS1 Technology Digest of Technical Papers

- [21] G. Elert (2004) . Resistivity of Aluminium. http://hypertextbook.com/facts/2004/ValPolyakov.shtml